Simulate the design, Simulate with ip functional simulation models, Simulate the design –3 – Altera ASI MegaCore Function User Manual

Page 12: Simulate with ip functional simulation models –3

Chapter 2: Getting Started

2–3

Design Flow

January 2014

Altera Corporation

Asynchronous Serial Interface (ASI) MegaCore Function User Guide

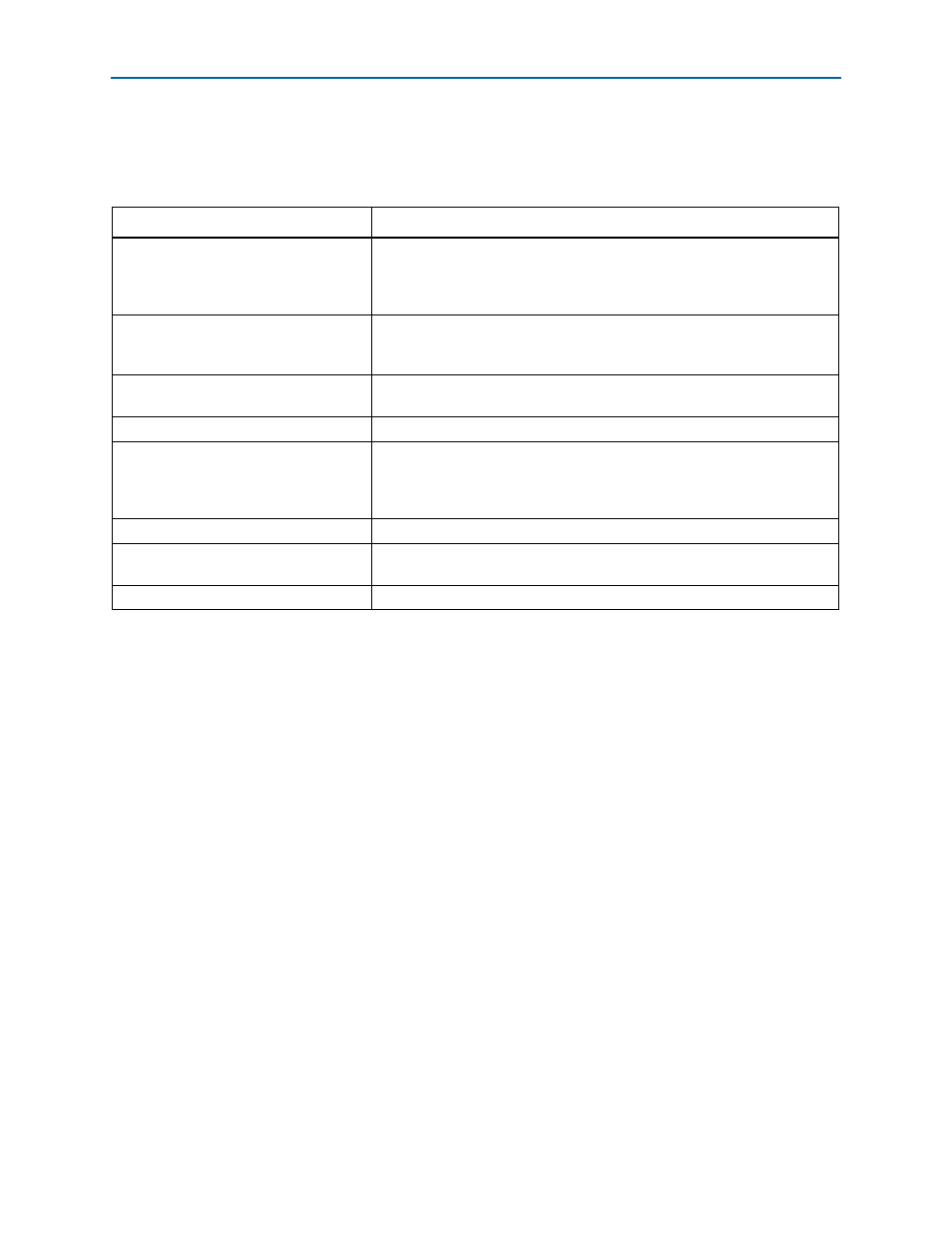

Table 2–1

describes the generated files and other files that may be in your project

directory. The names and types of files specified in the summary vary based on

whether you created your design with VHDL or Verilog HDL.

You can now integrate your custom MegaCore function variation into your design

and simulate and compile.

Simulate the Design

This section describes the following simulation techniques:

■

Simulate with IP Functional Simulation Models

■

Simulate with the ModelSim Simulator

■

Simulating in Third-Party Simulation Tools Using NativeLink

Simulate with IP Functional Simulation Models

You can simulate your design using the MegaWizard-generated VHDL and Verilog

HDL IP functional simulation models.

You can use the IP functional simulation model with any Altera-supported VHDL or

Verilog HDL simulator. To use the IP functional simulation model, create a suitable

testbench.

f

For more information on IP functional simulation models, refer to the

hapter in volume 3 of the Quartus II Handbook.

Table 2–1. Generated Files

File Name

Description

<variation name>.v or .vhd

A MegaCore function variation file, which defines a VHDL or Verilog HDL

description of the custom MegaCore function. Instantiate the entity defined by

this file inside of your design. Include this file when compiling your design in

the Quartus II software.

<variation name>.cmp

A VHDL component declaration file for the MegaCore function variation. Add

the contents of this file to any VHDL architecture that instantiates the

MegaCore function.

<variation name>.bsf

Quartus II symbol file for the MegaCore function variation. You can use this file

in the Quartus II block diagram editor.

<variation name>.html

MegaCore function report file.

<variation name>.ppf

This XML file describes the MegaCore pin attributes to the Quartus II Pin

Planner. MegaCore pin attributes include pin direction, location, I/O standard

assignments, and drive strength. If you launch IP Toolbench outside of the Pin

Planner application, you must explicitly load this file to use Pin Planner.

<variation name>.vo or .vho

VHDL or Verilog HDL IP functional simulation model.

<variation name>_bb.v

A Verilog HDL black-box file for the MegaCore function variation. Use this file

when using a third-party EDA tool to synthesize your design.

<variation name>.qip

Contains Quartus II project information for your MegaCore function variations.