Serializer, Gx transceivers, Receiver – Altera ASI MegaCore Function User Manual

Page 17: Transceiver, Serializer –2 gx transceivers –2, Receiver –2, Transceiver –2

4–2

Chapter 4: Functional Description

Receiver

Asynchronous Serial Interface (ASI) MegaCore Function User Guide

January 2014

Altera Corporation

Serializer

The serializer converts a 10-bit parallel word into a serial data output format. A 10-bit

shift register loaded at the word rate from the encoder and unloaded at the bit rate of

the LVDS output buffer is implemented for that function. You should use a PLL that

multiplies a 27-MHz reference clock by ten to provide the bit-rate clock and enables

jitter-controlled ASI transmit serialization.

GX Transceivers

For GX-based devices, in the MegaWizard Plug-In Manager you can select either a

soft-logic transceiver or a GX transceiver. If you are using GX transceivers, the

transmitter has a FIFO buffer, oversampler, and a transceiver, which replace the

soft-logic serializer.

f

For more information on the Stratix IV transceiver, refer to

Receiver

The receiver comprises the following elements:

■

■

■

■

■

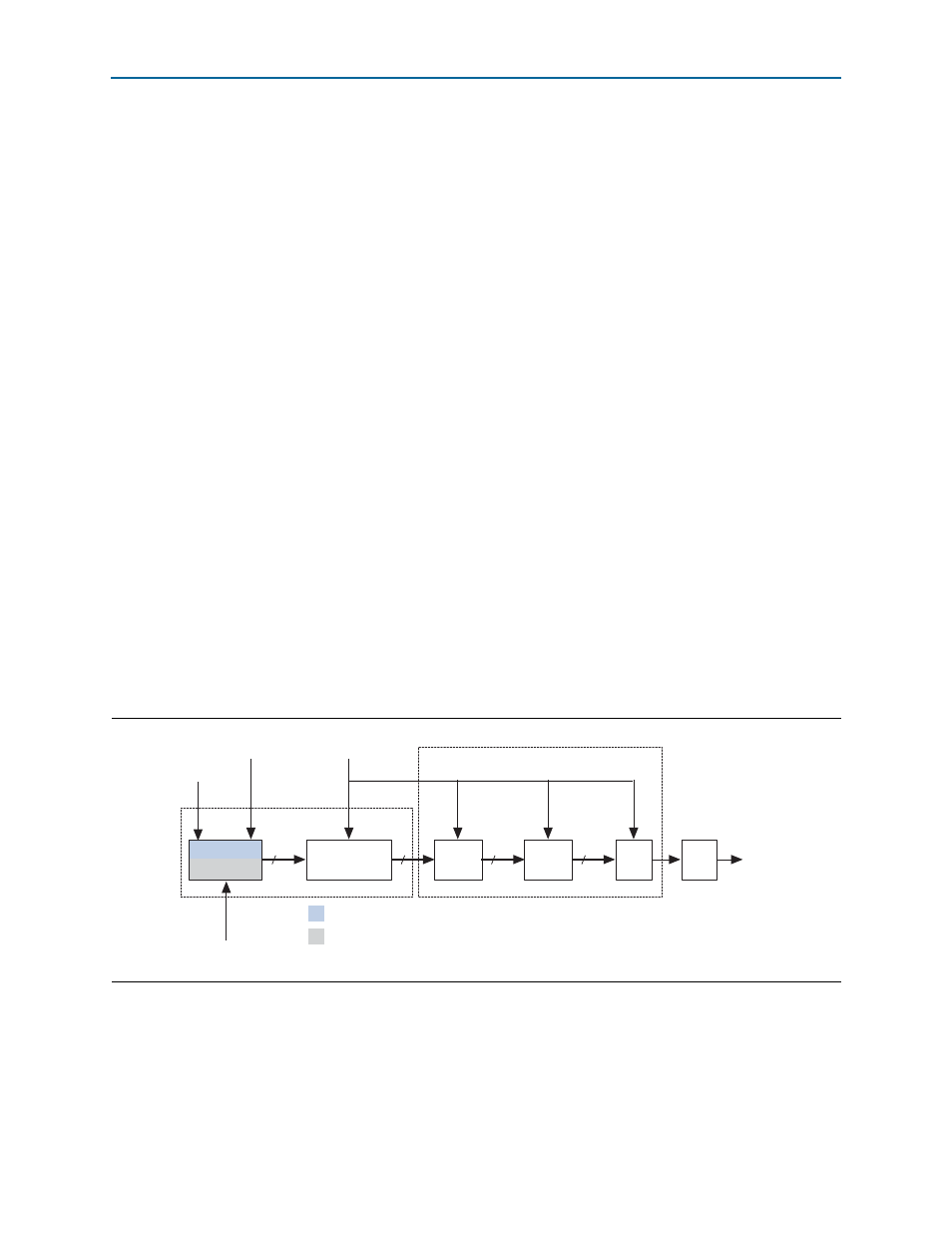

Figure 4–2

shows the ASI receiver.

Transceiver

The transceiver can be either a deserializer for soft-logic implementations or a GX

transceiver.

Figure 4–2. ASI Receiver

8B10B

Decoder

Oversampling

Interface

LVDS I/O

Serial Data

Deserializer

Transceiver

GX-based devices only

Soft-logic transceiver implementations only

10

337.5-MHz

Clock -90

135 MHz

Clock

Protocol Blocks

337.5-MHz

Clock

10

10

8

Transceiver

Word

Aligner

Sync.

FSM

Packet

Sync.

Parallel

Data

Out

o