Altera ASI MegaCore Function User Manual

Page 25

A–4

Appendix A: Constraints

Minimize Timing Skew

Asynchronous Serial Interface (ASI) MegaCore Function User Guide

January 2014

Altera Corporation

The following code is an example of a constraint, which you can set using the

Quartus II Assignment Editor:

set_location_assignment PIN_99 -to asi_rx0

set_location_assignment LC_X32_Y17_N0 -to

"asi_rx:u_rx0|asi_megacore_top:asi_megacore_top_inst|asi_receive:asi

rx_gen.u_rx|serdes_s2p:u_s2p|sample_a[0]"

set_location_assignment LC_X33_Y17_N0 -to

"asi_rx:u_rx0|asi_megacore_top:asi_megacore_top_inst|asi_receive:asi

rx_gen.u_rx|serdes_s2p:u_s2p|sample_b[0]"

set_location_assignment LC_X32_Y17_N1 -to

"asi_rx:u_rx0|asi_megacore_top:asi_megacore_top_inst|asi_receive:asi

rx_gen.u_rx|serdes_s2p:u_s2p|sample_c[0]"

set_location_assignment LC_X33_Y17_N1 -to

"asi_rx:u_rx0|asi_megacore_top:asi_megacore_top_inst|asi_receive:asi

rx_gen.u_rx|serdes_s2p:u_s2p|sample_d[0]"

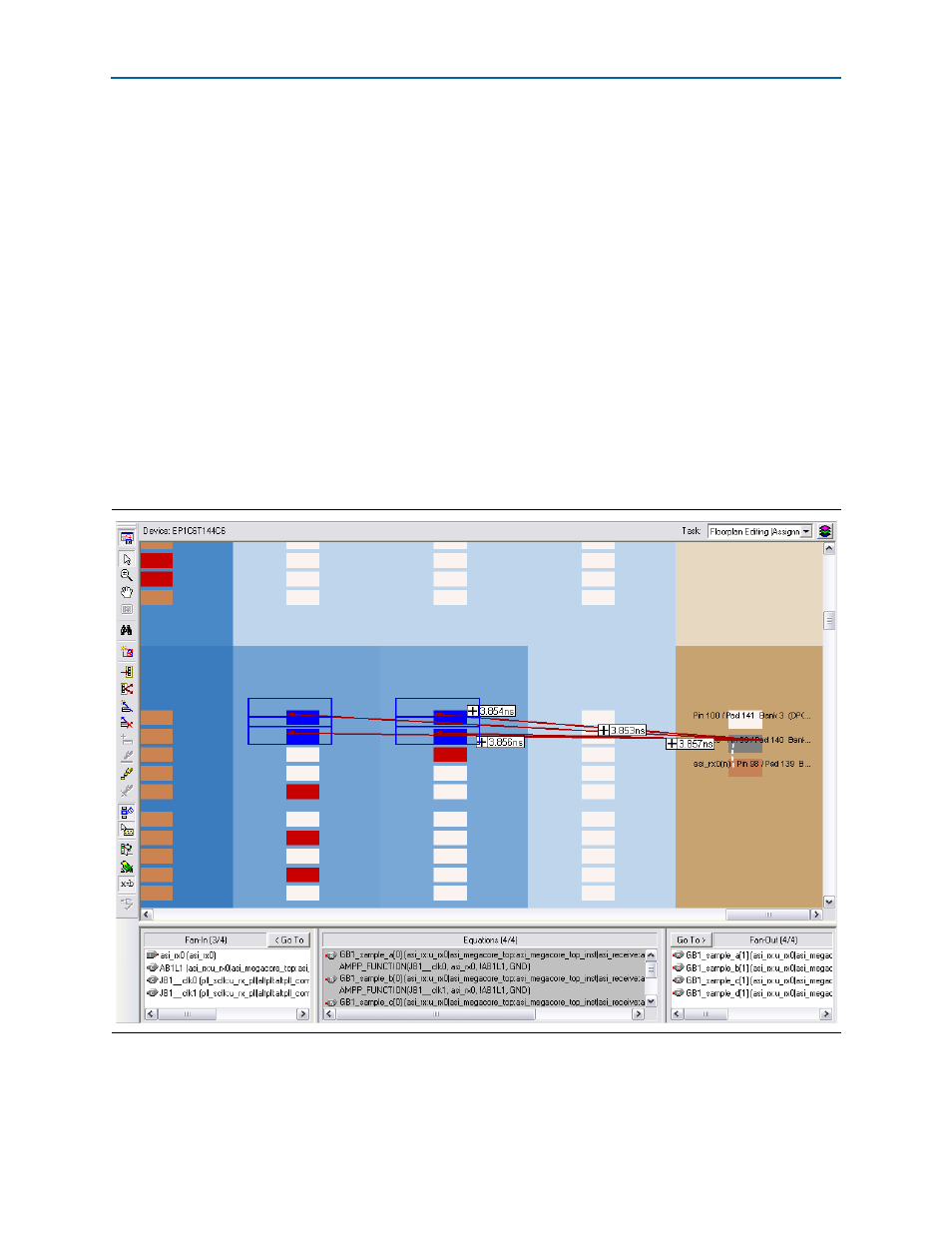

Figure A–1

shows the placement of these registers in the Quartus II chip planner

floorplan.

Figure A–1. Register Placement