Cic ip core signals, Cic ip core signals -11 – Altera CIC MegaCore Function User Manual

Page 27

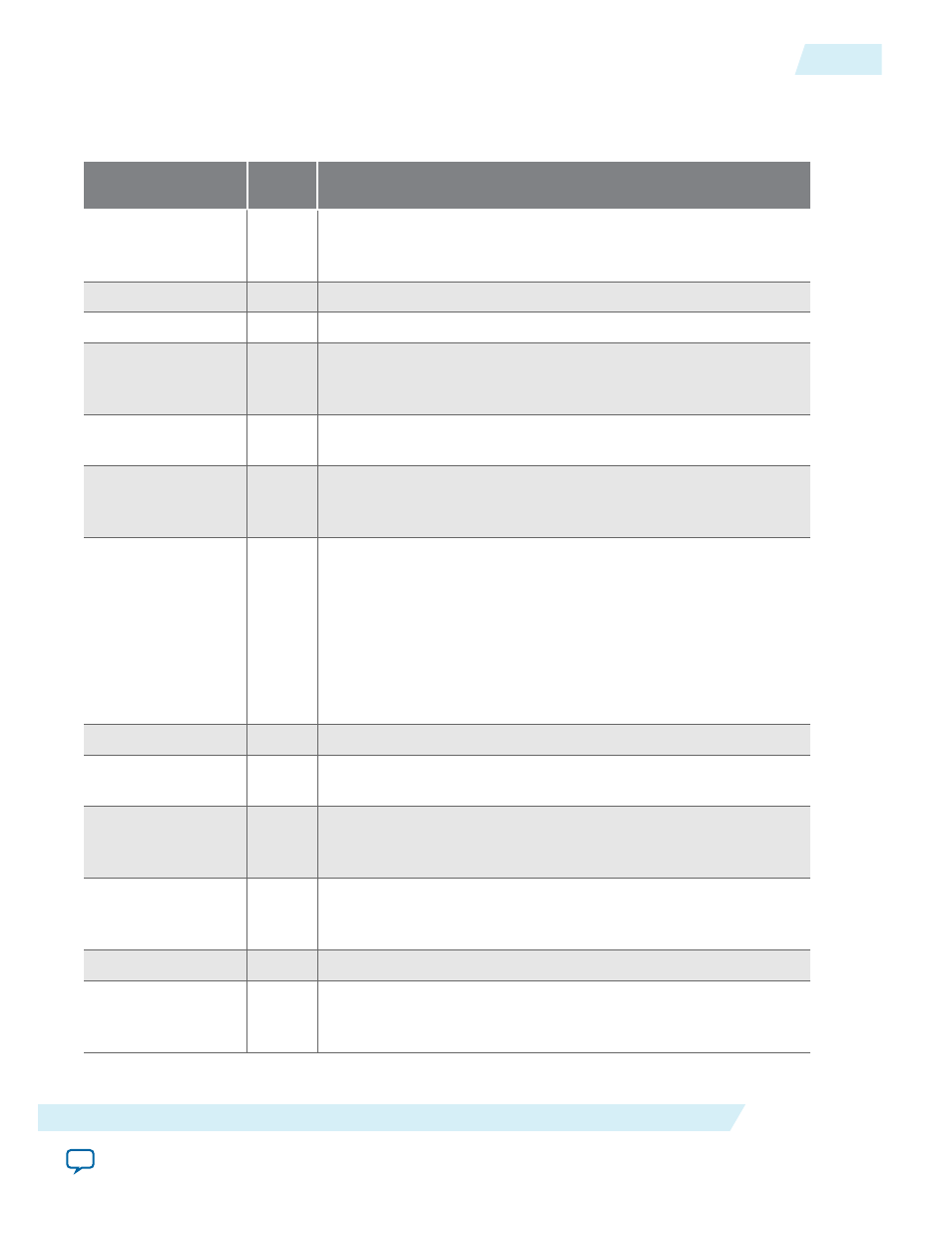

CIC IP Core Signals

Table 3-4: CIC IP Core Signals

Signal

Directio

n

Description

av_st_in_data

Output In Qsys systems, this Avalon-ST-compliant data bus includes all

the Avalon-ST input data signals. For multi-interface designs

Interface 0 is in the MSB; Interface N is the LSB.

clk

Input

Clock signal for all internal registers.

clken

Input

Optional top-level clock enable.

reset_n

Input

Active low reset signal. You must always reset the CIC MegaCore

function before receiving data. If not, the CIC filter may produce

unexpected results because of feedback signals.

in_data

Input

Sample input. For multiple input cases, the input data ports are

in0_data

,

in1_data

, and so on.

in_endofpacket

Input

Marks the end of the incoming sample group. For N channels, the

end of packet signal must be high when the sample belonging to

the last channel, channel N-1, is presented at

in_data

.

in_error

Input

Error signal indicating Avalon-ST protocol violations on input

side:

• 00: No error

• 01: Missing start of packet

• 10: Missing end of packet

• 11: Unexpected end of packet

Other types of error are also marked as 11.

in_ready

Output Indicates when the IP core can accept data.

in_startof-

packet

Input

Marks the start of the incoming sample group. The start of packet

is interpreted as a sample from channel 0.

in_valid

Input

Asserted when data at

in_data

is valid. When

in_valid

is not

asserted, processing is stopped until valid is re-asserted. If

clken

is

0,

in_valid

is not be asserted.

av_st_out_data

Output In Qsys systems, this Avalon-ST-compliant data bus includes all

the Avalon-ST output data signals. For multi-interface designs

Interface 0 is in the MSB; Interface N is the LSB.

out_channel

Output Specifies the channel whose result is presented at

out_data

.

out_data

Output Filter output. The data width depends on the parameter settings.

For multiple output cases, the output data ports are named as

out0_data

,

out1_data

, and so on.

UG-CIC

2014.12.15

CIC IP Core Signals

3-11

CIC IP Core Functional Description

Altera Corporation