Avalon-st interface data transfer timing, Packet data transfers, Avalon-st interface data transfer timing -12 – Altera CIC MegaCore Function User Manual

Page 28: Packet data transfers -12

Signal

Directio

n

Description

out_endofpacket

Output Marks the end of the outgoing result group. If '1', a result

corresponding to channel N-1 is output, where N is the number of

channels.

out_error

Output Error signal indicating Avalon-ST protocol violations on source

side:

• 00: No error

• 01: Missing start of packet

• 10: Missing end of packet

• 11: Unexpected end of packet

Other types of errors may also be marked as 11.

out_ready

Input

Asserted by the downstream module if it is able to accept data.

out_startof-

packet

Output Marks the start of the outgoing result group. If '1', a result

corresponding to channel 0 is output.

out_valid

Output Asserted by the IP core when there is valid data to output.

rate

Input

This signal is available when the variable rate change factor option

is enabled. You can use it to change the decimation or interpola‐

tion rate during run time. It has the size Ceil(log

2

(maximum rate))

.

Avalon-ST Interface Data Transfer Timing

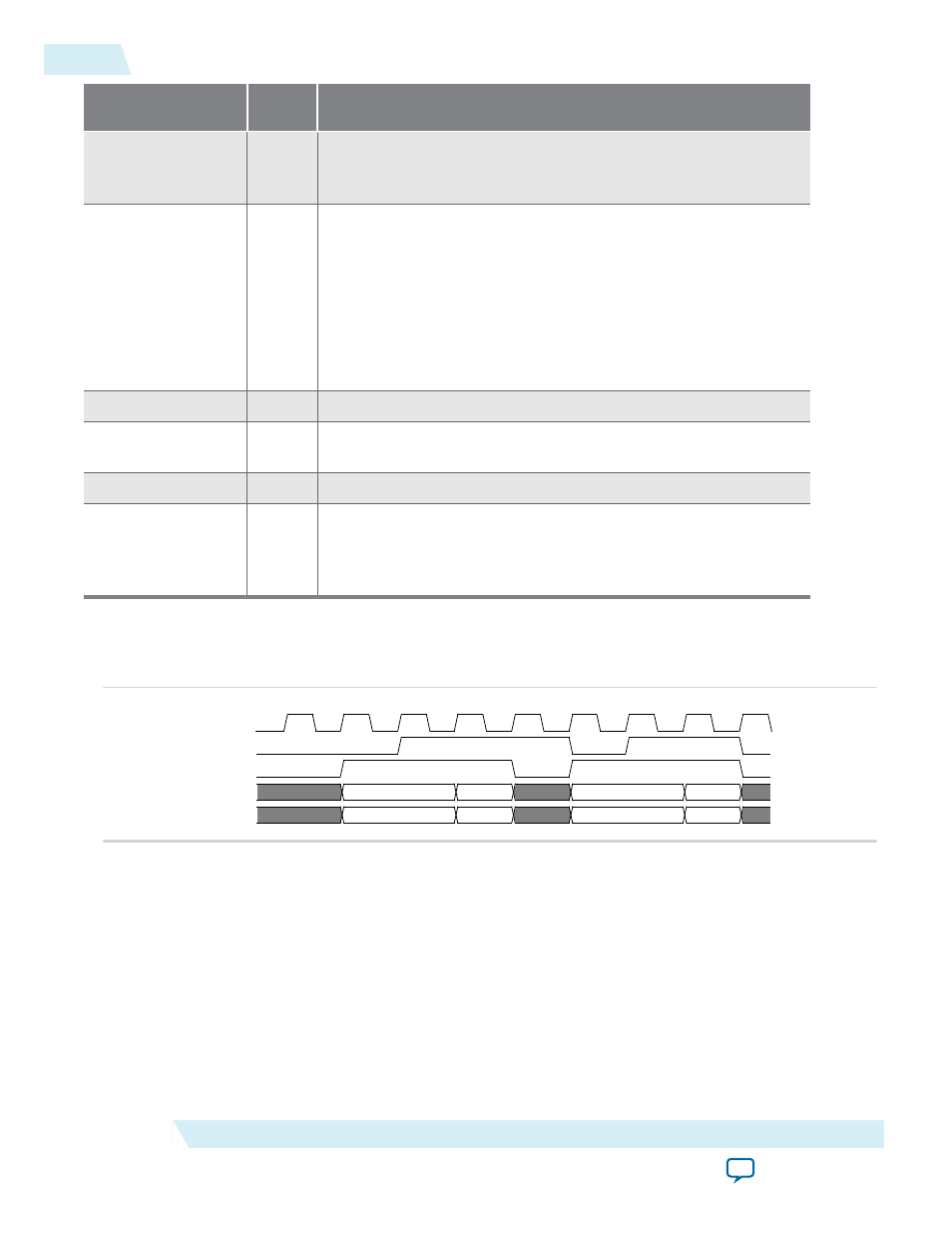

Figure 3-7: Avalon-ST Interface Timing with READY_LATENCY=0

D

o

D

1

D

2

0

1

2

3

5

6

7

8

4

clk

ready

valid

error

data

00

00

00

00

D

2

The source provides data and asserts

valid

on cycle 1, even though the sink is not ready. The source waits

until cycle 2, when the sink does assert

ready

, before moving onto the next data cycle. In cycle 3, the

source drives data on the same cycle and because the sink is ready to receive it, the transfer occurs

immediately. In cycle 4, the sink asserts

ready

, but the source does not drive valid data.

Packet Data Transfers

A beat is the transfer of one unit of data between a source and sink interface. This unit of data may consist

of one or more symbols and makes it is possible to support modules that convey more than one piece of

information about each valid cycle.

Packet data transfers are used for multichannel transfers. Two additional signals (

startofpacket

and

endofpacket

) are defined to implement the packet transfer.

3-12

Avalon-ST Interface Data Transfer Timing

UG-CIC

2014.12.15

Altera Corporation

CIC IP Core Functional Description