Cic ip core performance and resource utilization – Altera CIC MegaCore Function User Manual

Page 5

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP

core. Altera does not verify that the Quartus II software compiles IP core versions older than the previous

version. The Altera IP Release Notes lists any exceptions.

Related Information

•

•

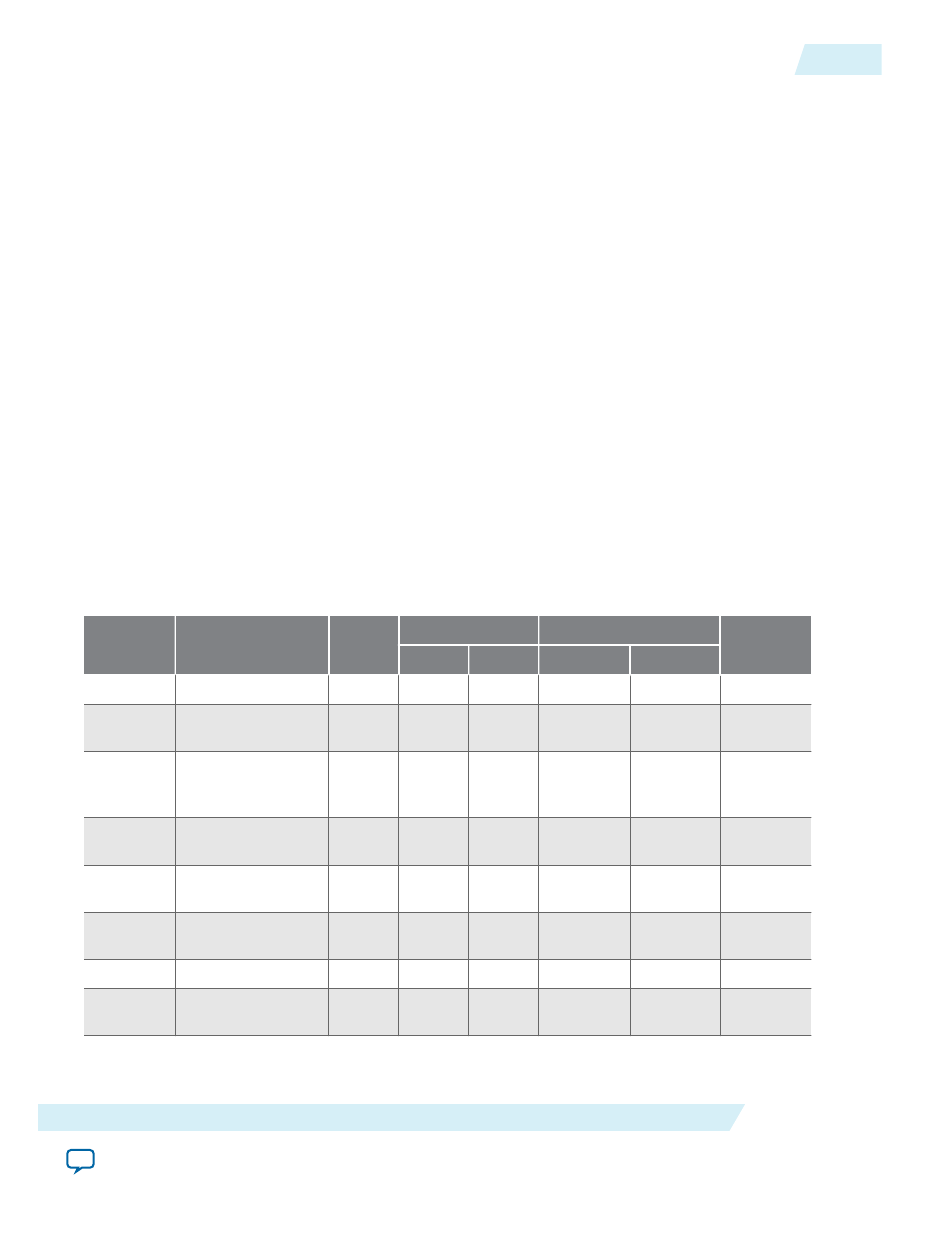

CIC IP Core Performance and Resource Utilization

The following parameters apply:

• Number of stages: 8

• Rate change factor: 8

• Differential delay: 1

• Integrator data storage: Memory (whenever possible)

• Differentiator data storage: Memory (whenever possible)

• Input data width: 16

• Output data width: Full precision

• Output rounding: No rounding

The target f

MAX

is 1 GHz.

Table 1-3: CIC IP Core Performance

Typical performance using the Quartus II software with the Arria V (5AGXFB3H4F40C4), Cyclone V

(5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices

Device

Filter Type

ALM

Memory

Registers

f

MAX

(MHz)

M10K

M20K

Primary

Secondary

Arria V Decimator

493

2

--

1,149

5

207.34

Arria V Decimator 5

Channels

1,162

2

--

3,749

6

207

Arria V Decimator 5

Channels 3

Interfaces

911

37

--

1,722

6

255

Arria V Decimator

Hogenauer Pruning

352

1

--

785

12

304

Arria V Decimator

Trunction

463

2

--

1,055

5

198.69

Arria V Decimator Variable

Rate Change

919

37

--

1,730

7

256

Arria V Interpolator

326

1

--

728

18

320

Arria V Interpolator 5

Channels

762

1

--

2,369

27

288

UG-CIC

2014.12.15

CIC IP Core Performance and Resource Utilization

1-3

About The CIC IP Core

Altera Corporation