Altera Double Data Rate I/O User Manual

Page 5

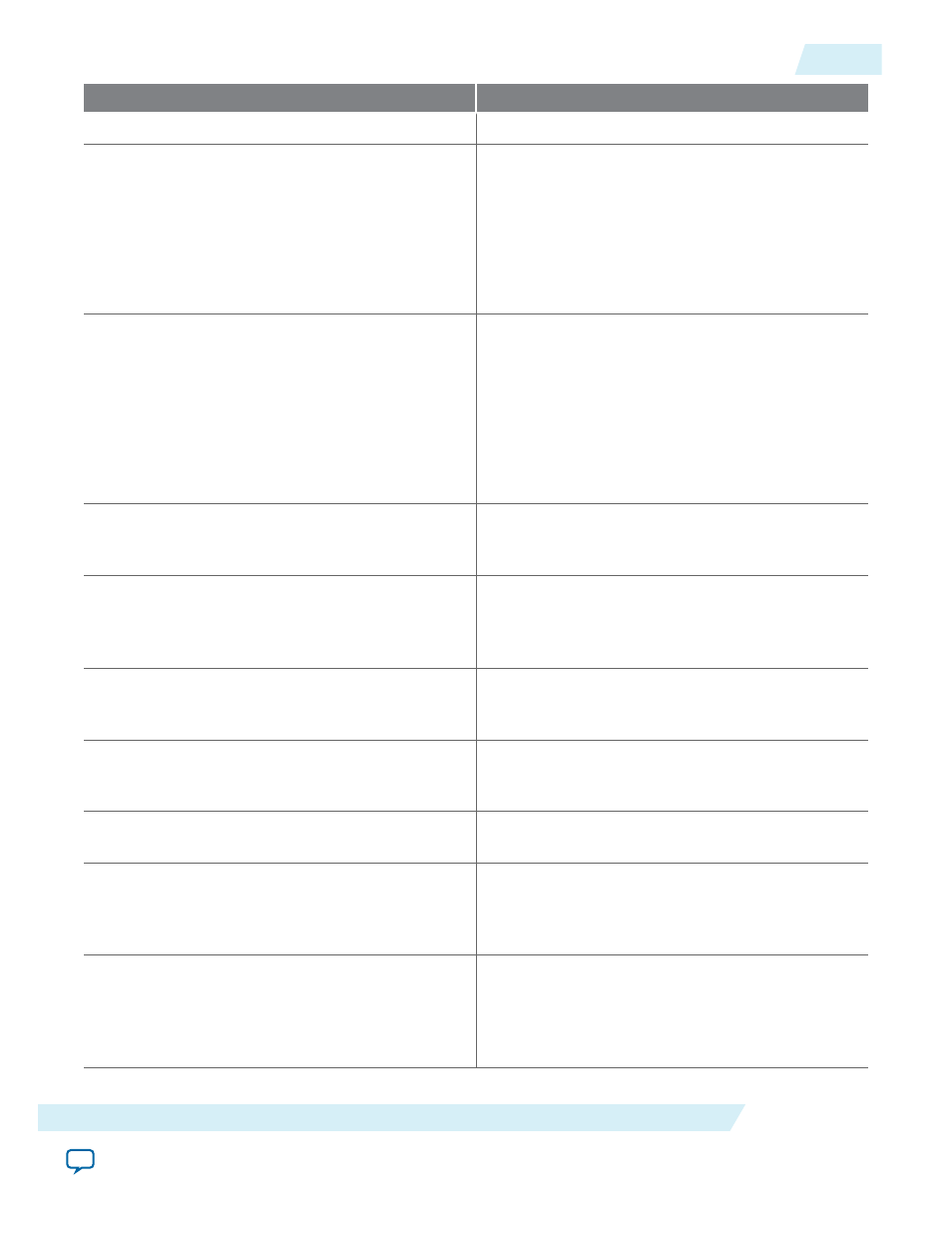

Parameter

Description

Width: (bits)

Specify the width of the data buses.

Asynchronous clear and asynchronous set ports

Select Use ‘aclr’ port for asynchronous clear (aclr).

Select Use ‘aset’ port for asynchronous preset (aset)

.

If you are not using any of the asynchronous clear

options, select Not used and specify whether

registers should power up high or low by turning

on/off Registers power up high.

Synchronous clear and synchronous set ports

Select Use ‘sclr’ port for synchronous clear (sclr).

Select Use ‘sset’ port for synchronous preset (sset).

If you are not using any of the synchronous clear

options, select Not used.

The synchronous reset option is available for

Arria GX, Stratix III, Stratix II, Stratix II GX,

Stratix, Stratix GX, HardCopy II, and HardCopy

Stratix devices only.

Invert ‘padio’ port

The ‘padio’ port is inverted whenever driven as an

output. This option is available for Cyclone III and

Cyclone II devices only.

Use ‘inclocken’ and ‘outclocken’ ports

Turn on this option to add a clock enable port to

control when data input and output are clocked in.

This signal prevents data from being passed

through.

Use output enable port

Turn on this option to create an output enable input

port (

oe

) to control when the data is set out to the

dataout

port.

Use oe_out port to connect to tri-state output

buffer(s)

Output enable for the bidirectional

padio

port. This

port is available for Stratix III and Cyclone III

devices only.

Register ‘oe’ port

Turn on this option to register the output-enable

(

oe

) input port.

Delay switch-on by a half clock cycle

Turn on this option to use an additional

oe

register.

When the additional

oe

register is used, the output

pin is held at high impedance for an extra half clock

cycle after the

oe

port goes high.

Use ‘combout’ port

Use the optional data port

combout

. The

combout

port sends data to the core, bypassing the DDR I/O

input registers. For bidirectional operation, you

must enable the

dataout_h

and

dataout_l

ports,

the

combout

port, or both.

UG-DDRMGAFCTN

2015.01.23

ALTDDIO Parameter Settings

5

Double Data Rate I/O (ALTDDIO_IN, ALTDDIO_OUT, and ALTDDIO_BIDIR) IP Cores User Guide

Altera Corporation