Prototyping walkthrough files – Altera PCI Development Kit, Cyclone II Edition Getting Started User Manual

Page 29

Altera Corporation

Core Version a.b.c variable

2–19

May 2005

PCI Development Kit, Cyclone II Edition Getting Started User Guide

Getting Started

f

“Software Installation” on page 2–4

for more information.

To simulate your design using this walkthrough, you need the Model

Technology ModelSim simulator version 6.0 or later, which is not

included with the kit.

1

The reference design’s DDR2 memory simulation model is only

available in Verilog HDL, and the reference design is in VHDL.

Mixed VHDL and Verilog HDL simulation may require

additional ModelSim licenses.

Prototyping Walkthrough Files

The prototyping walkthrough uses reference design source files,

simulation files, and compilation files that you copy from the PCI

Development Kit, Cyclone II Edition CD-ROM installation directory to your

working directory.

Table 2–2

describes the reference design source files used in the

walkthrough. These files are located in the <path>\cycloneii_pci_kit-

v1.0.0\reference_design\vhdl

directory.

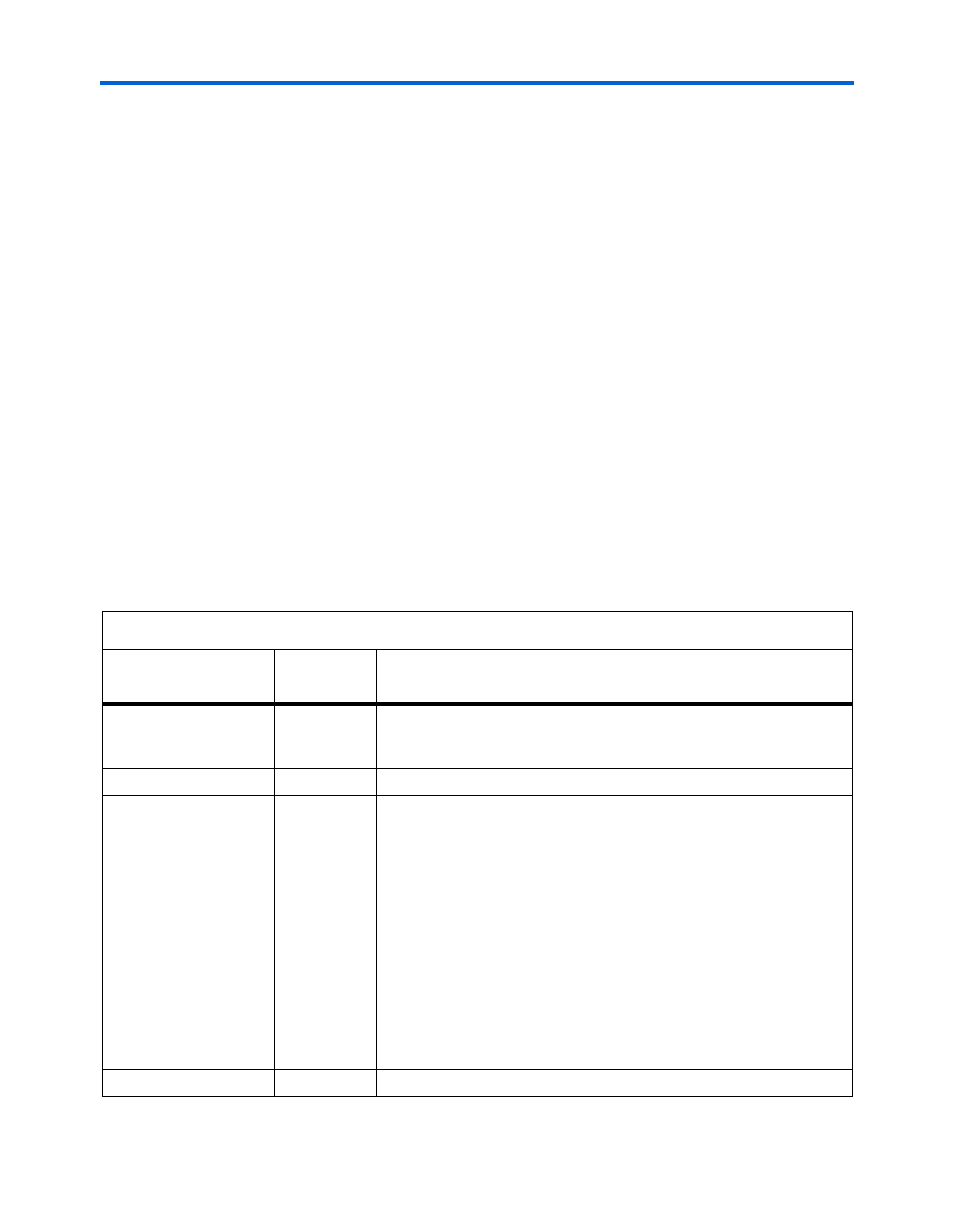

Table 2–2. Prototyping Walkthrough Reference Design Source Files (Part 1 of 2)

File

Subdirectory

(1)

Description

cpd_top.vhd

—

The top-level file that instantiates the PCI and DDR2 SDRAM cores

and the local design. Refer to AN 390: PCI-to-DDR2 SDRAM

Reference Design for a description of the local design.

vhdl_components.vhd —

The VHDL component instantiation templates.

pci_top.vhd

pci_mt64

This wrapper file implements the pci_mt64 core. The file was

generated with the PCI Compiler wizard and the following settings:

●

VHDL output file

●

64-bit master/target MegaCore function (pci_mt64)

●

Device ID is set to 0x0009

●

Revision ID is set to 0x1

●

Subsystem ID is set to 0xE102

●

Subsys Vendor ID is set to 0x1172

●

BAR0 is a 1-MByte memory

●

BAR1 is a 64-MByte prefetchable memory

●

All other parameters are at the default values

For more information, refer to the PCI Compiler User Guide.

backend.vhd

pci_local

The top level of the local PCI interface.