Altera Temperature Sensor User Manual

Page 3

Temperature Sensing Operation for Arria V, Arria V GZ, Stratix IV, and Stratix V

Devices

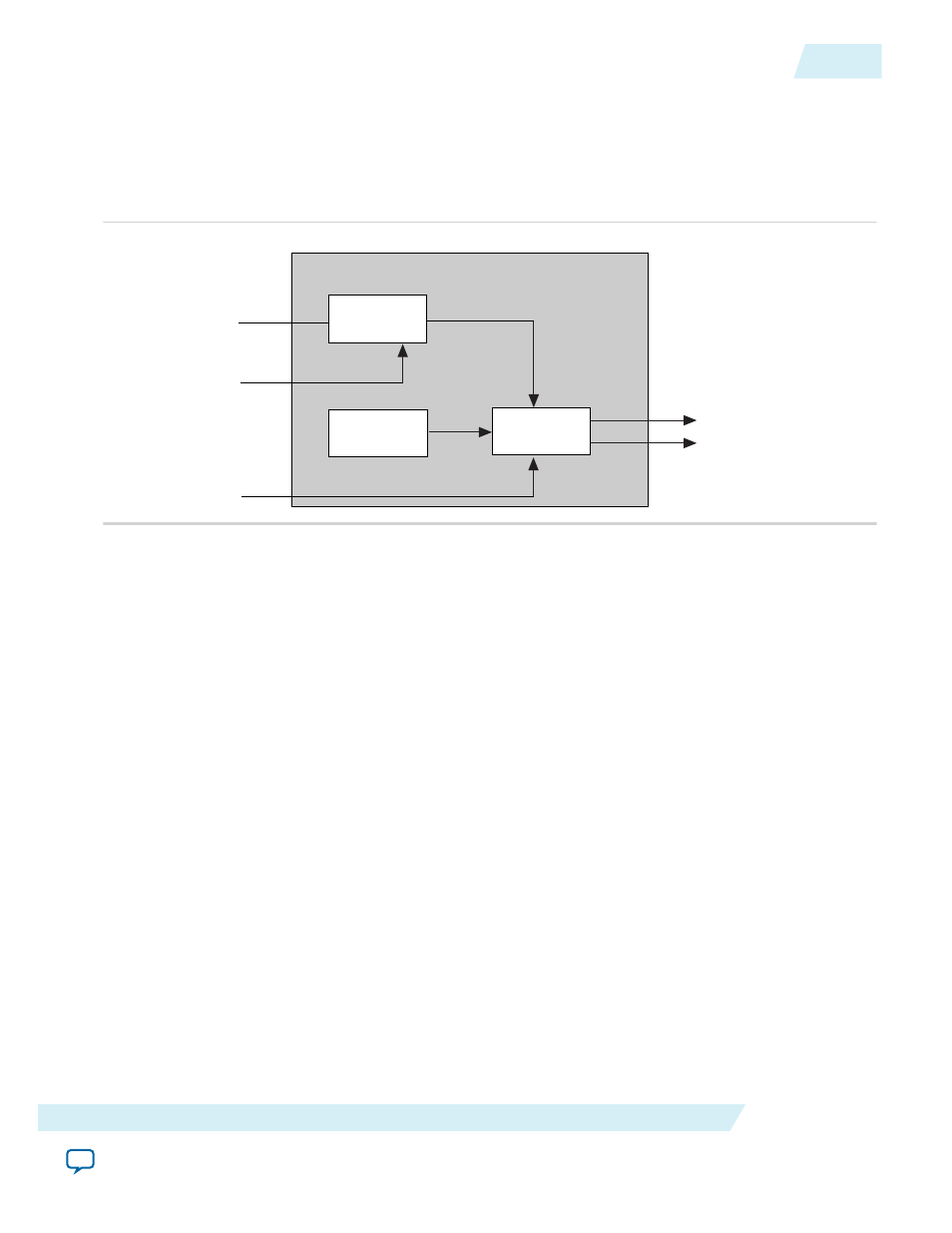

Figure 2: Altera Temperature Sensor Block Diagram

This figure shows the top-level ports and the basic building blocks of the Altera Temperature Sensor IP

core.

ce

tsdcalo[7:0]

clr

tsdcaldone

clk

Altera Temperature Sensor IP Core

TEMPERATURE

SENSOR

adcclk

CLOCK

DIVIDER

ADC

oe

The Altera Temperature Sensor IP core runs at the frequency of the

clk

signal. The

clk

signal can run at a

frequency of 80 MHz and below. The clock divider divides the

clk

signal to 1 MHz or less to feed the

ADC. You can set the value of the clock divider using the Altera Temperature Sensor IP core parameter

editor.

The

ce

signal connects to the output enable (

oe

) port of the clock divider block. Assert the

ce

signal to

enable the Altera Temperature Sensor IP core. When you deassert the

ce

signal, the IP core disables the

ADC, and maintains the previous values of the

tsdcalo[7..0]

and

tsdcaldone

signals unless you assert

the

clr

signal, or reset the device. The

clr

signal is asynchronous, and you must assert the

clr

signal at

least one clock cycle of the

adcclk

signal to clear the output ports.

Enabling the ADC allows you to measure the device temperature only once. To perform another tempera‐

ture measurement, assert the

clr

signal, or reset the device. The

clr

signal is asynchronous, and you must

assert the

clr

signal at least one clock cycle of the ADC

clk

signal to clear the output ports.

Note: When you choose not to create the

ce

port, the IP core connects the

ce

port to VCC. In this case,

the ADC circuitry is always enabled. Altera recommends that you disable the ADC by deasserting

the

ce

signal when the ADC is not in use to reduce power consumption.

During device power-up or when you assert the asynchronous

clr

signal, the Altera Temperature Sensor

IP core sets the

tsdcaldone

port to

0

and the

tsdcalo[7:0]

signal to

11010101

or

0xD5

. After 10 clock

cycles of the

adcclk

signal, the Altera Temperature Sensor IP core asserts the

tsdcaldone

signal to

indicate that the temperature sensing operation is complete and that the value of the

tsdcalo[7:0]

signal

is valid. The value of the

tsdcalo[7:0]

signal corresponds to the device temperature range. For more

information about the value of

tsdcalo[7:0]

signals, refer to the Related Information. To start another

temperature sensing operation, assert the

clr

signal for at least one clock cycle of the

adcclk

signal, or

reset the device.

UG-01074

2015.05.04

Temperature Sensing Operation for Arria V, Arria V GZ, Stratix IV, and Stratix V

Devices

3

Altera Temperature Sensor IP Core User Guide

Altera Corporation