Altera Arria V SoC Development Board User Manual

Page 41

Chapter 2: Board Components

2–33

Components and Interfaces

July 2014

Altera Corporation

Reference Manual

lists the FMC port B pin assignments, signal names, and functions.

C27

LMK_SYSREF_FMC_N

—

2.5-V CMOS

Alternate mezzanine-bound SYSREF signal (from LMK

device)

C26

LMK_SYSREF_FMC_P

—

2.5-V CMOS

Alternate mezzanine-bound SYSREF signal (from LMK

device)

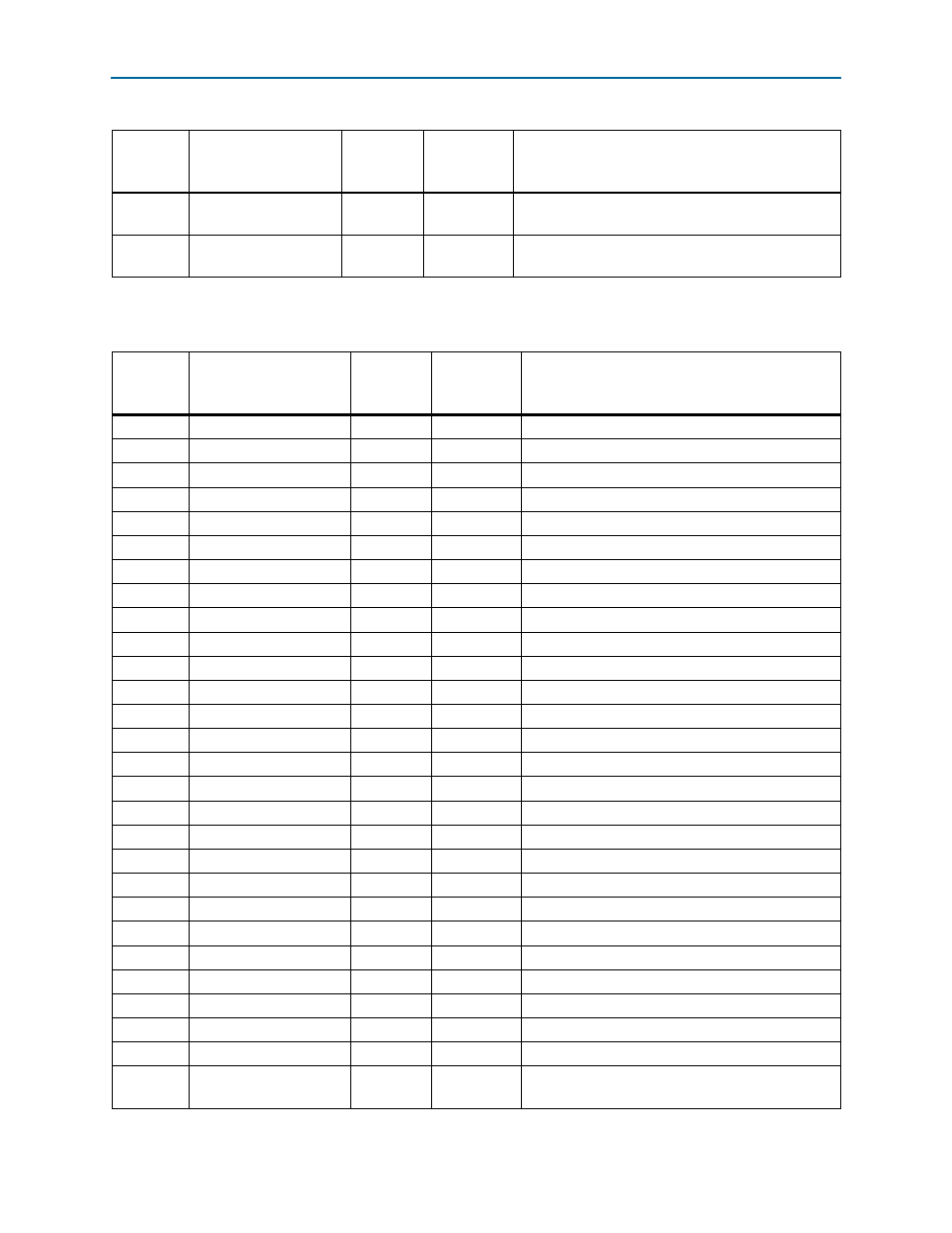

Table 2–21. FMC Port A Pin Assignments, Schematic Signal Names, and Functions (Part 5 of 5)

Board

Reference

(J26)

Schematic

Signal Name

Arria V SoC

Pin Number

I/O Standard

Description

Table 2–22. FMC Port B Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 4)

Board

Reference

(J4)

Schematic Signal Name

Arria V SoC

Pin Number

I/O Standard

Description

D1

FMCB_C2M_PG

—

2.5-V CMOS

Power good output

H4

FMCB_CLK_M2C_P0

C34

LVDS

Clock input 0

H5

FMCB_CLK_M2C_N0

D34

LVDS

Clock input 0

G2

FMCB_CLK_M2C_P1

G34

LVDS

Clock input 1

G3

FMCB_CLK_M2C_N1

H34

LVDS

Clock input 1

C3

FMCB_DP_C2M_N0

AU36

PCML

Transmit channel

A23

FMCB_DP_C2M_N1

AN36

PCML

Transmit channel

A27

FMCB_DP_C2M_N2

AL36

PCML

Transmit channel

A31

FMCB_DP_C2M_N3

AG36

PCML

Transmit channel

C2

FMCB_DP_C2M_P0

AU37

PCML

Transmit channel

A22

FMCB_DP_C2M_P1

AN37

PCML

Transmit channel

A26

FMCB_DP_C2M_P2

AL37

PCML

Transmit channel

A30

FMCB_DP_C2M_P3

AG37

PCML

Transmit channel

C7

FMCB_DP_M2C_N0

AW36

PCML

Receive channel

A3

FMCB_DP_M2C_N1

AP38

PCML

Receive channel

A7

FMCB_DP_M2C_N2

AM38

PCML

Receive channel

A11

FMCB_DP_M2C_N3

AH38

PCML

Receive channel

C6

FMCB_DP_M2C_P0

AW37

PCML

Receive channel

A2

FMCB_DP_M2C_P1

AP39

PCML

Receive channel

A6

FMCB_DP_M2C_P2

AM39

PCML

Receive channel

A10

FMCB_DP_M2C_P3

AH39

PCML

Receive channel

C34

FMCB_GA0

J33

2.5-V CMOS

FMC geographical address 0

D35

FMCB_GA1

R30

2.5-V CMOS

FMC geographical address 1

D4

FMCB_GBTCLK_M2C_P0

AG32

LVDS

Transceiver reference clock 0

D5

FMCB_GBTCLK_M2C_N0

AG33

LVDS

Transceiver reference clock 0

B20

FMCB_GBTCLK_M2C_P1

AE31

LVDS

Transceiver reference clock 1

B21

FMCB_GBTCLK_M2C_N1

AE32

LVDS

Transceiver reference clock 1

E18

FMCB_GPIO0

F32

2.5-V CMOS

FMC general purpose IO bit 0 (part of the partially

populated HPS connector signal group)