Sensoray 526 User Manual

Page 27

27

Notes.

1.

In “Latch on read” mode data from the counter is latched on the read access to the Counter

data low word register. Thus the low word has to be always read first in this mode.

2.

In “Latch on event” mode data from the counter is latched by the event(s) selected with bits

[12:10] of Counter Control/Status register.

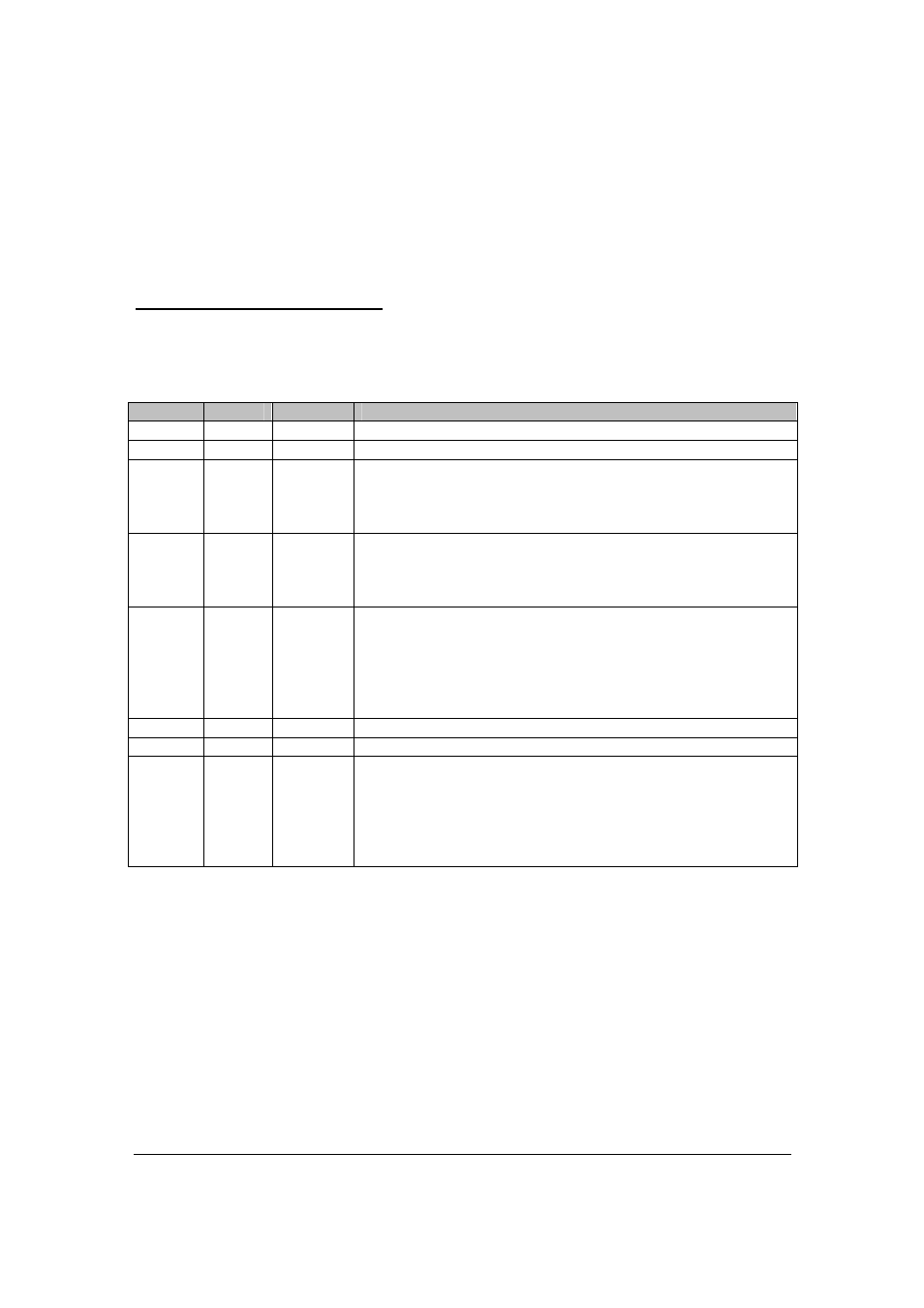

Counter Control/Status Register

0x18 – counter 0,

0x20 – counter 1,

0x28 – counter 2,

0x30 – counter 3.

Bits

Type

Default

Description

[15]

WO

0

Counter reset. Writing a 1 resets the counter and RTGL to 0.

[14]

WO

0

Counter load. Writing a 1 loads a counter from PR0.

[13]

WO

0

Counter arm. Writing a 1 enables count to start at the rising

edge of Count Enable signal (only relevant when Hardware

Count Enable source is set to “INDEX

↑

to

↓

”, bits [6:5] of Mode

Register).

[12:10]

WO

000

Latch event select:

[12] – latch data on interrupt timer expiration;

[11] – latch data on INDEX

↑

;

[10] – latch data on INDEX

↓

.

[9:6]

WO

0000

Interrupt enable. Writing a 1 enables an interrupt from the

corresponding event (Note 1):

[9] – RO;

[8] – INDEX

↑

;

[7] – INDEX

↓

;

[6] – ERROR.

[5]

RO

0

INDEX real time status. Write has no effect.

[4]

RO

0

COUT real time status. Write has no effect.

[3:0]

RR

0000

Captured events status bits (Note 2). Writing a 1 resets

corresponding signal and status bit to 0:

[3] – RCAP;

[2] – ICAP+;

[1] – ICAP-;

[0] – ECAP.

Notes:

1.

Interrupt for a particular counter has to be enabled in Interrupt Enable Register as well.

2.

All bits in this group are captured events, i.e. they are set to 1 when a corresponding event

occurs, and keep this value until reset to 0. Corresponding bit in the Interrupt Status Register

is set as soon as any of the captured events status bits is set to 1. The bit(s) set to 1 must

be reset to 0 to enable subsequent interrupt detection.