Emif control registers – Sundance SMT365 User Manual

Page 9

Version 2.3

Page 9 of 28

SMT365 User Manual

It is safest to wait for the configuration to complete. Note that comports will appear to

be "not ready" until the FPGA has been configured.

The FPGA programming algorithm is not described here. It can be found in the boot

code.

EMIF Control Registers

The DSP has two external memory interfaces (EMIF) that are 64 bits wide and 16

bits wide.

The DSP contains several registers that control the external memory interface

(EMIF). A full description of these registers can be found in the

The standard bootstrap will initialise these registers to use the following resources:

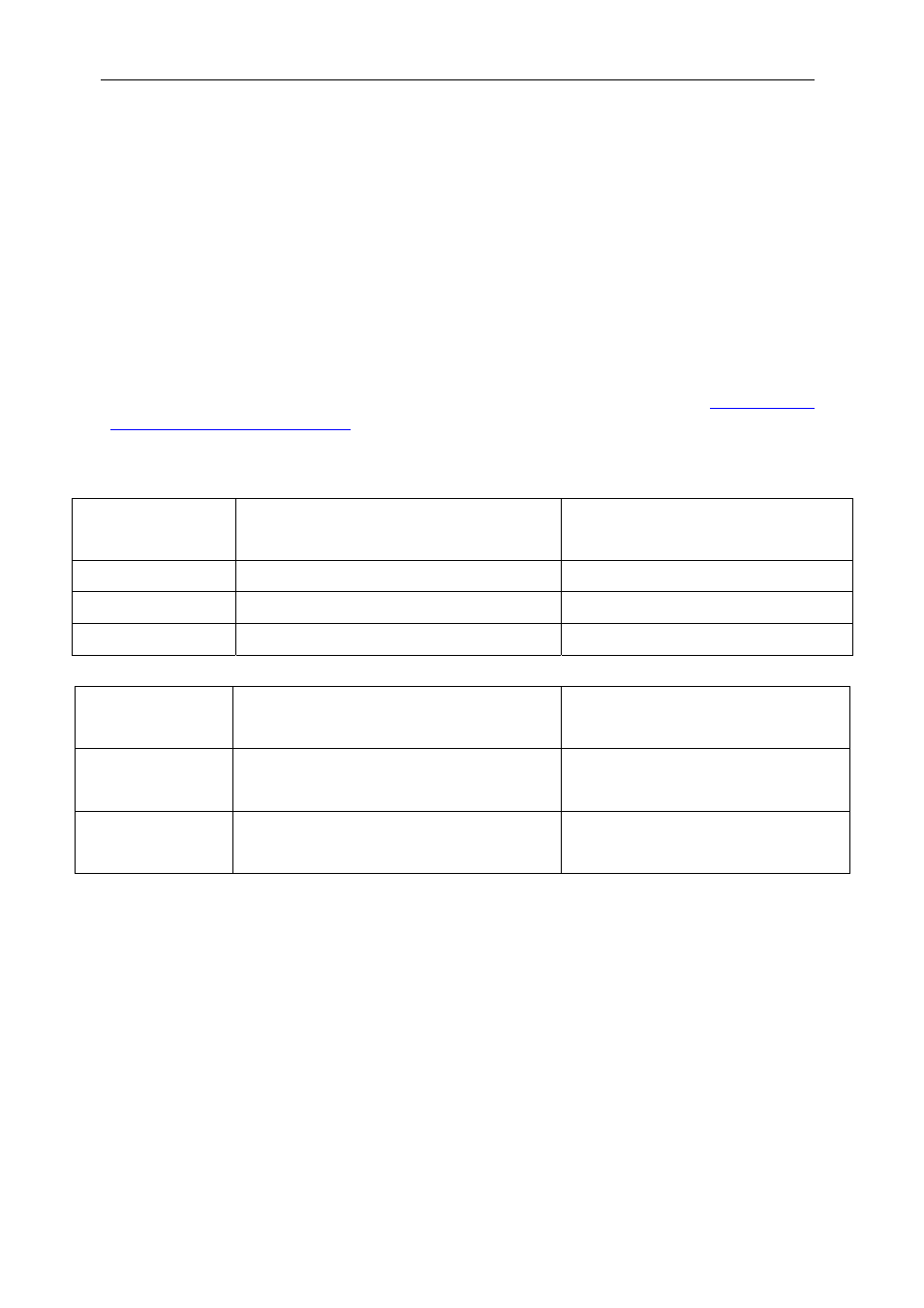

Memory space

(EMIFA)

Resource Address

range

Internal program memory (1MB)

0x00000000 - 0x000FFFFF

CE0

ZBTRAM (2x 8MB sections)

0x80000000 - 0x807FFFFF

CE1

Virtex

0x90000000 - 0x900FFFFF

Memory space

(EMIFB)

Resource Address

range

CE1 1

st

/3

rd

section of flash

(2MB each)

0x64000000 – 0x641FFFFF

CE2 2

nd

/4

th

section of flash

(2MB each)

0x68000000 – 0x681FFFFF