Altera MAX 10 Clocking and PLL User Manual

Page 74

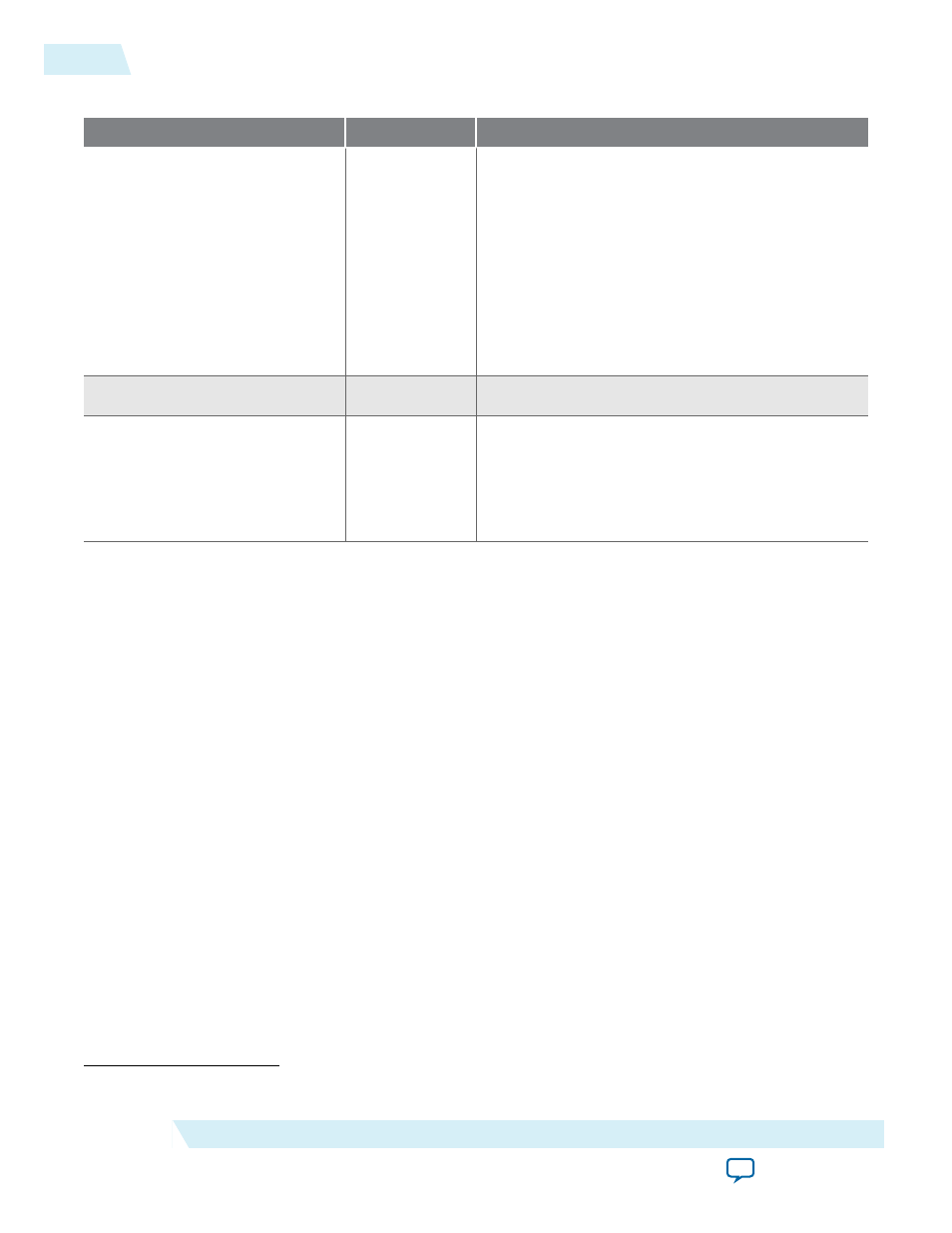

Table 6-8: ALTPLL Output Ports for MAX 10 Devices

Port Name

(11)

Condition

Description

activeclock

Optional

Specifies which clock is the primary reference clock

when the clock switchover circuit initiates.

If the

inclk0

is in use, the

activeclock

port goes

low. If the

inclk1

is in use, the

activeclock

port

goes high.

You can set the PLL to automatically initiate the

clock switchover when the primary reference clock

is not toggling correctly, or you can manually

initiate the clock switchover using the

clkswitch

input port.

c[]

Required

The clock output of the PLL.

clkbad[]

Optional

clkbad1

and

clkbad0

ports check for input clock

toggling.

If the

inclk0

port stops toggling, the

clkbad0

port

goes high. If the

inclk1

port stops toggling, the

clkbad1

port goes high.

(11)

Replace the brackets,

[]

, in the port name with an integer to get the exact name (for example,

c0

and

c1

).

6-8

ALTPLL Ports and Signals

UG-M10CLKPLL

2014.12.15

Altera Corporation

ALTPLL IP Core References