Altera Embedded Peripherals IP User Manual

Page 34

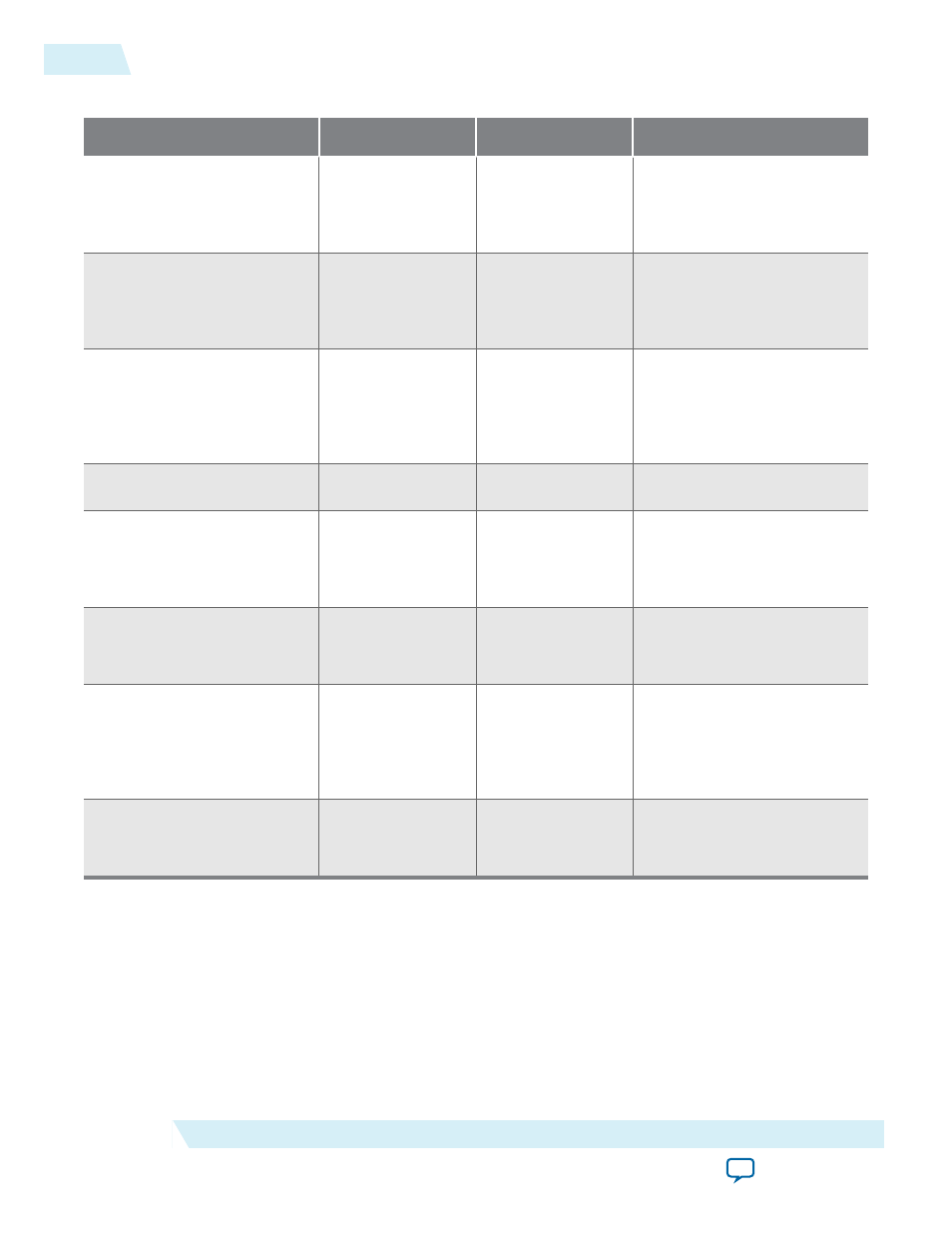

Table 3-4: Avalon-MM Slave Interface Signals

Signal

Width

Direction

Description

avs_read

1

Input

Avalon-MM read control.

Asserted to indicate a read

transfer. If present,

readdata

is required.

avs_write

1

Input

Avalon-MM write control.

Asserted to indicate a write

transfer. If present,

writedata

is required.

avs_byteenable

dqm_width

Input

Enables specific byte lane(s)

during transfer. Each bit

corresponds to a byte in

avs_

writedata

and

avs_

readdata

.

avs_address

controller_addr_

width

Input

Avalon-MM address bus.

avs_writedata

sdram_data_width

Input

Avalon-MM write data bus.

Driven by the bus master

(bridge unit) during write

cycles.

avs_readdata

sdram_data_width

Output

Avalon-MM readback data.

Driven by the

altera_spi

during read cycles.

avs_readdatavalid

1

Output

Asserted to indicate that the

avs_readdata

signals

contains valid data in

response to a previous read

request.

avs_waitrequest

1

Output

Asserted when it is unable to

respond to a read or write

request.

3-4

Interface

UG-01085

2014.24.07

Altera Corporation

Tri-State SDRAM