Avalon-mm slave, Read behavior, Avalon-mm slave -7 – Altera Embedded Peripherals IP User Manual

Page 93

16 clock multi-cycle path on the output side. Furthermore, divider of 1 is an unlikely system, if the UART

is clocked at 125 MHz, the resulting baud rate would be 7.81 Mbps.

Avalon-MM Slave

The Avalon-MM Slave has the following configuration:

Table 9-10: Avalon-MM Slave Configuration

Feature

Configuration

Bus Width

32-bit

Burst Support

No burst support. Interconnect is expected to

handle burst conversion

Fixed read and write wait time

0 cycles

Fixed read latency

1 cycle

Fixed write latency

0 cycles

Lock support

No

Note: The Avalon-MM interface is intended to be a thin, low latency layer on top of the registers.

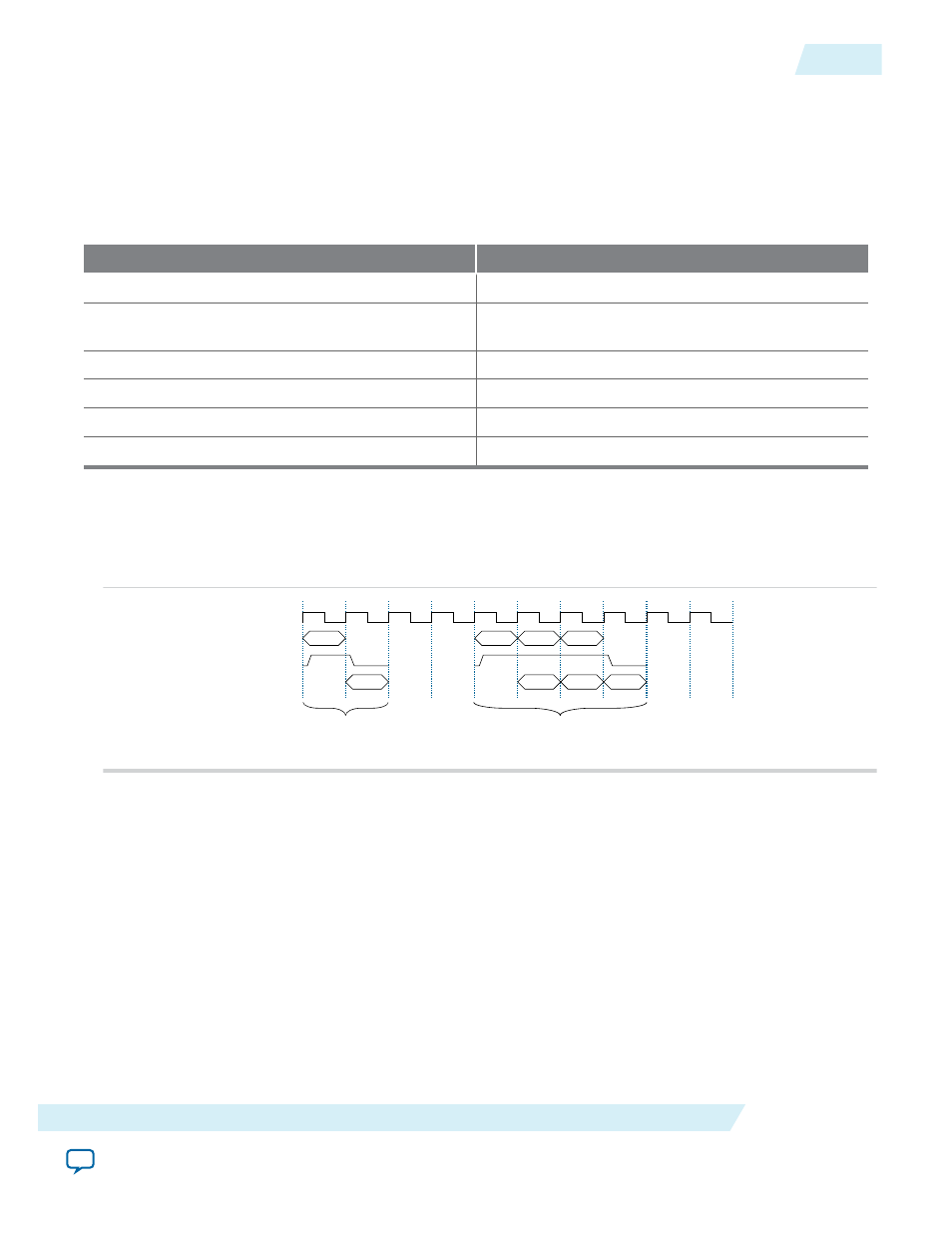

Read behavior

Figure 9-3: Reading UART over Avalon-MM

addr1

addrF

addrF

addrF

data1

data2

data3

data4

addr

read

readdata

Polling Status

Reading from

RX FIFO

0

1

2

3

4

5

6

7

8

9

UG-01085

2014.24.07

Avalon-MM Slave

9-7

16550 UART

Altera Corporation