Altera POS-PHY Level 4 IP Core User Manual

Page 114

B–2

Appendix B: Sharing PLLs for Multicore Designs

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

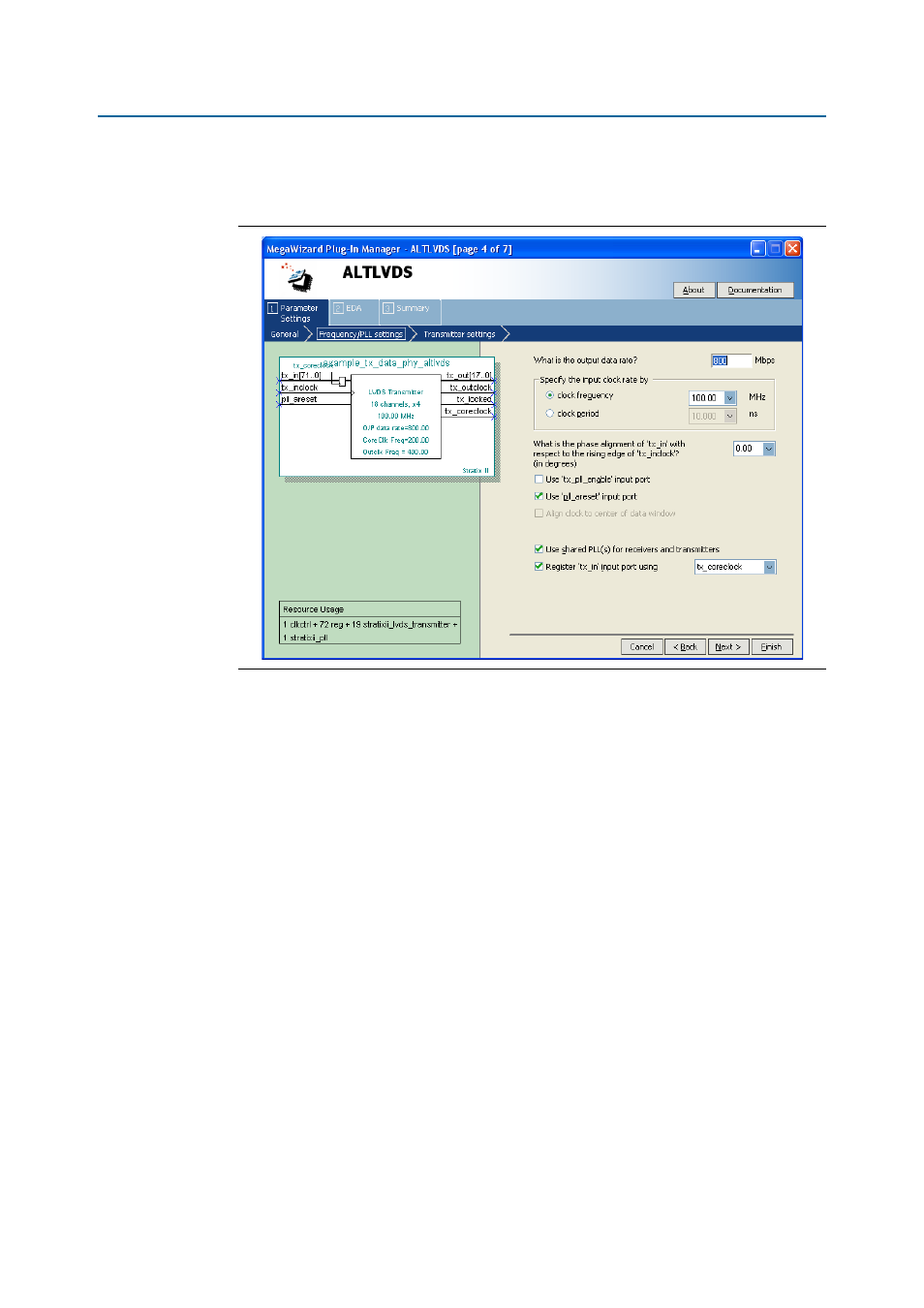

4. Open the transmitter’s LVDS parameter editor and change the input clock

frequency to <number of Mbps>/2 (refer to

5. In the top-level design, connect the PLL reset signals (cH_rx_pll_areset and

cH_tx_pll_areset

) and the rdclk to the trefclk signal.

To share a PLL between two transmitters, ensure the input frequencies are matched

and connect the trefclk signals together.

1

If the receiver PLL is configured as real-time configurable, it does not automatically

merge with the transmitter PLL. Use the following assignment to force the merging of

the receiver and transmitter PLLs:

set_instance_assignment -name FORCE_MERGE_PLL ON -from "<tx_pll>" -to

"<rx_pll>"

Figure B–2. Specify ALTLVDS Parameters