12 pld revision register, Table 6-13, Pld revision register – Artesyn MVME3100 Single Board Computer Installation and Use (June 2014) User Manual

Page 117

Memory Maps

MVME3100 Single Board Computer Installation and Use (6806800M28E)

117

PMC1P: PMC module 1 present. If cleared, there is no PMC module installed in site 1. If set, the

PMC module is installed.

PMC2P: PMC module 2 present. If cleared, there is no PMC module installed in site 2. If set, the

PMC module is installed.

PEP: PMCspan present. If cleared, there is no PMCspan module installed. If set, the PMCspan

module is installed.

RSVD: Reserved for future implementation.

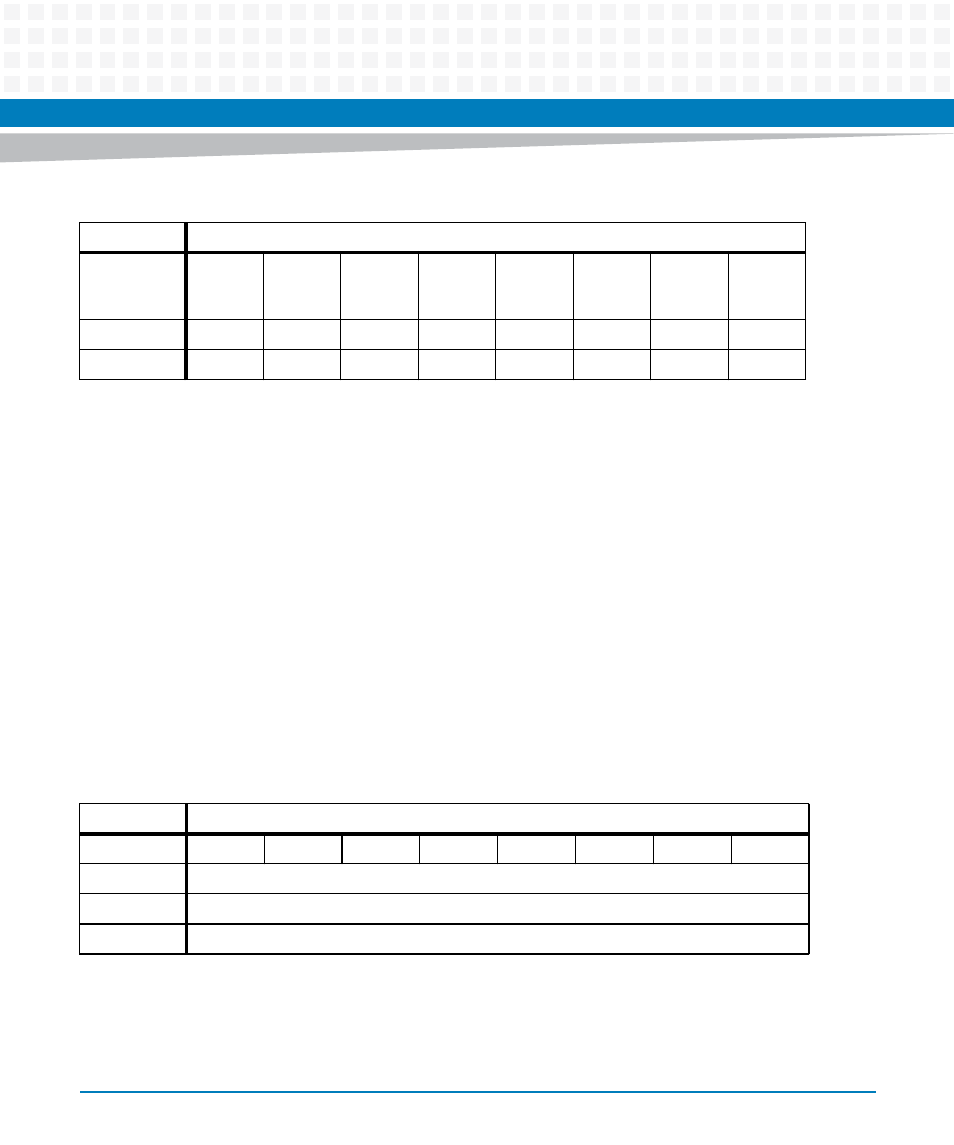

6.1.12 PLD Revision Register

The MVME3100 provides a PLD Revision register that may be read by the system software to

determine the current revision of the timers/registers PLD.

PLD_REV: 8-bit field containing the current timer/register PLD revision. The revision number

starts with 01.

FIELD

RS

V

D

RS

V

D

RS

V

D

RS

V

D

RS

V

D

PEP

PMC2P

PMC1P

OPER

R

R

R

R

R

R

R

R

RESET

0

0

0

0

0

X

X

X

Table 6-12 Presence Detect Register (continued)

REG

Presence Detect Register - 0xE2000008

Table 6-13 PLD Revision Register

REG

PLD Revision Register - 0xE2000009

BIT

7

6

5

4

3

2

1

0

FIELD

PLD_REV

OPER

R

RESET

01