Programming details – Artesyn MVME3100 Single Board Computer Installation and Use (June 2014) User Manual

Page 126

Programming Details

MVME3100 Single Board Computer Installation and Use (6806800M28E)

126

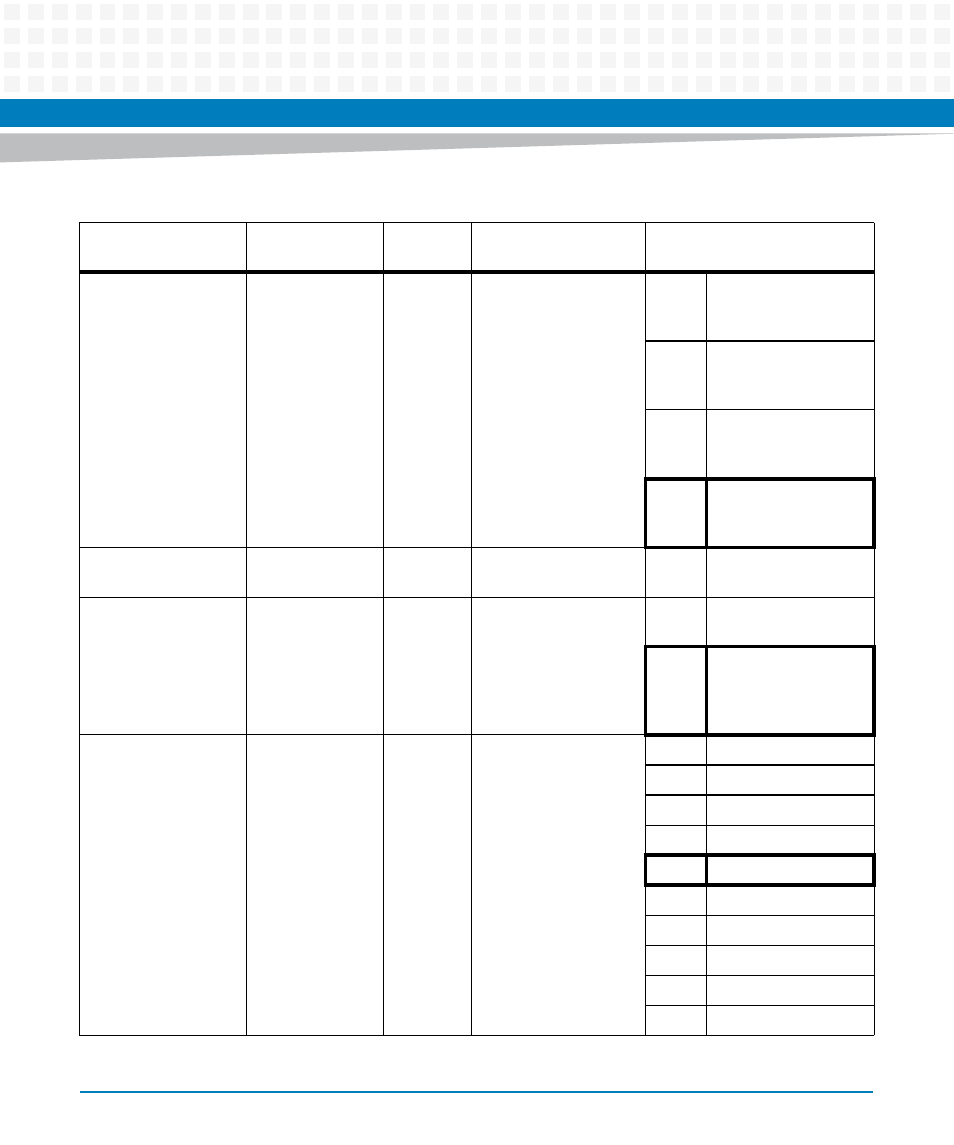

TSEC2_

TXD [6:5]

Resistors

11

Local Bus Output Hold

Configuration

00

0 added buffer delays

(0 added buffer delays

for LALE)

01

3 added buffer delays

(1 added buffer delay

for LALE)

10

2 added buffer delays

(1 added buffer delay

for LALE)

11

1 added buffer delay

(0 added buffer delays

for LALE)

TSEC2_

TXD [2:4]

Fixed

000

RapidIO Device ID (3

lower-order bits)

000

Unconnected Inputs

LA27

Resistor

1

CPU Boot

Configuration

0

CPU boot hold off

mode

3

1

e500 core boots

without waiting for

configuration by an

external master

LA [28:31]

PLD logic

0011 for

100 MHz

PCI bus

0101 for

66 MHz

PCI bus

CCB Clock PLL Ratio

(CCB Clock : SYSCLK)

0000

16:1

0010

2:1

0011

3:1

0100

4:1

0101

5:1

0110

6:1

1000

8:1

1001

9:1

1010

10:1

1100

12:1

Table 7-1 MPC8540 Power-on Reset Configuration Settings (continued)

MPC8540 Signal

Select Option

Default

Setting

Description

State of Bit vs Function

1