BECKHOFF PHY User Manual

Page 9

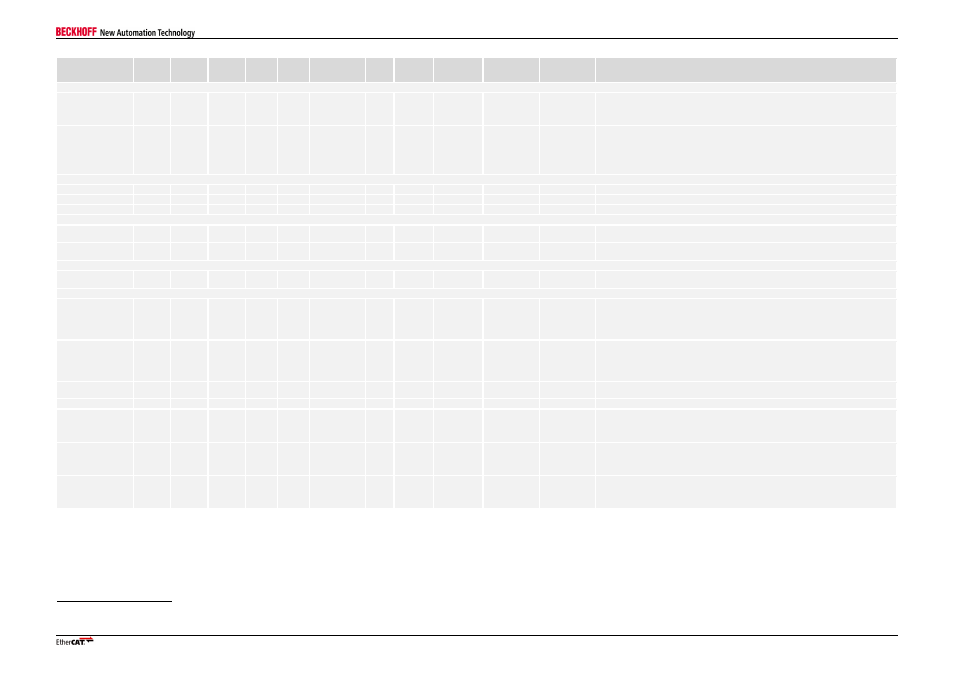

Example Ethernet PHYs

Slave Controller

– Application Note PHY Selection Guide

6

Vendor / Device

ET1200

suitable

ET1100

suitable

IP Core

suitable

# Ports

Basic

HW

test

6

TX_CLK fixed

phase

7

PHY

addr.

8

PHY addr.

offset

9

Link loss

reaction time

Enhanced Link

Detection

Auto-TX-Shift

(IP Core only)

Comments

Renesas

µPD60610/µPD60611

-

-

X

1

no

0/8/16

/24

0

3 x RX_ER

(120 ns)

not necessary

required

Link loss reaction time configurable via MII management interface. Enhanced Link Detection cannot be

used with more than 1 port, because PHY addresses are not consecutive.

MI Link detection and configuration can only be enabled for tolerant IP Cores (starting with

V2.4.3/V2.04d and V3.0.2/V3.00c)

µPD60620/µPD60621

X

X

X

2

yes (Data sheet)

0/8/16

/24+1

0

3 x RX_ER

(120 ns)

not necessary

Link loss reaction time configurable via MII management interface; Set P1TXCL=0 for fixed TX_CLK

phase shift. Enhanced Link Detection cannot be used with more than 1 port, because PHY addresses

are not consecutive.

EtherCAT support starts with order number UPD60620AGK-GAK-AX / UPD60621AGK-GAK-AX.

MI Link detection and configuration can only be enabled for tolerant IP Cores (starting with

V2.4.3/V2.04d and V3.0.2/V3.00c)

SMSC/Microchip

LAN8187

-

-

X

1

no (Vendor)

0-31

0

provisionally

required

Link signal depends on PHY address.

LAN8700

-

-

X

1

no (Vendor)

0-31

0

provisionally

required

Link signal depends on PHY address.

LAN8710

X

1

no

0-7

0

provisionally

provisionally

STMicroelectronics

STE101P

-

-

X

13

1

1-31

16

provisionally

provisionally

PHY addr. 0 = Isolate. MDC clock transition required to complete reset phase (MI Link Detection and

Configuration required). Link signal depends on PHY address.

STE802RT1A/B

-

-

1

yes (Vendor)

1-31

16

provisionally

PHY addr. 0 = Isolate. MDC clock transition required to complete reset phase (MI Link Detection and

Configuration required).

Teridian

78Q2123

78Q2133

X

1

0/1

0

provisionally

provisionally

PHY addr. 0 = Broadcast. Only for single port devices, because only one PHY address can be used.

Texas Instruments

DP83620/

DP83630/

DP83640

X

X

X

1

yes (Vendor)

1-31

ET1100/

ET1200: 0

IP: 16

250 µs (conf.

to ~1.3 µs)

required

PHY addr. 0 = Isolate. Do not use SCMII mode. Use LED_LINK for link detection. Reset controller

required if clock sourced by ESC.

ET1100/ET1200: if port 0 is used, set PHY addresses to 1-4, PHY address offset to 0, add CPLD/uC

for address conversion.

IP Core: Set PHY address offset = 16 and use PHY addresses 16-19.

DP83848

X

X

X

1

yes

yes (Vendor)

1-31

ET1100/

ET1200: 0

IP: 16

250 µs

required

PHY addr. 0 = Isolate. Use LED_LINK for link detection.

ET1100/ET1200: if port 0 is used, set PHY addresses to 1-4, PHY address offset to 0, add CPLD/uC

for address conversion. X1 must be stable for min. 167 µs, need reset controller if CLK25Out is used

and resets are connected.

IP Core: Set PHY address offset = 16 and use PHY addresses 16-19.

DP83849

X

X

X

2

yes (Vendor)

0-31

0

250 µs

required

Do not use SCMII mode. Use LED_LINK for link detection. X1 must be stable for min. 167 µs, need

reset controller if CLK25Out is used and resets are connected.

TLK100

-

-

X

1

no

0-31

0

500 µs

required

required

TX_CLK phase changes at each link up.

TLK105

X

X

X

1

yes (Data sheet)

0-31

0

200 µs (conf.

to <10 µs)

required

Fast Link Down mode with 10 µs reaction time is supported (requires configuration via MII

management, default is 200 µs). Recommended configuration for Fast Link Down mode in CR3:

enable Bit 3 (RX Error count) and Bit 0 (Signal/Energy loss).

MI Link detection and configuration must not be used, because register 9 is PHY specific.

TLK106

X

X

X

1

yes (Data sheet)

0-31

0

200 µs (conf.

to <10 µs)

required

Fast Link Down mode with 10 µs reaction time is supported (requires configuration via MII

management, default is 200 µs). Recommended configuration for Fast Link Down mode in CR3:

enable Bit 3 (RX Error count) and Bit 0 (Signal/Energy loss).

MI Link detection and configuration must not be used, because register 9 is PHY specific.

TLK110

X

X

X

1

yes (Data sheet)

0-31

0

200 µs (conf.

to <10 µs)

required

Fast Link Down mode with 10 µs reaction time is supported (requires configuration via MII

management, default is 200 µs). Recommended configuration for Fast Link Down mode in SWSCR3:

enable Bit 3 (RX Error count) and Bit 0 (Signal/Energy loss).

MI Link detection and configuration must not be used, because register 9 is PHY specific.

13

MI link detection and configuration required.