Ql5064, Local bus, Virtex fpga configuration – Sundance SMT407 User Manual

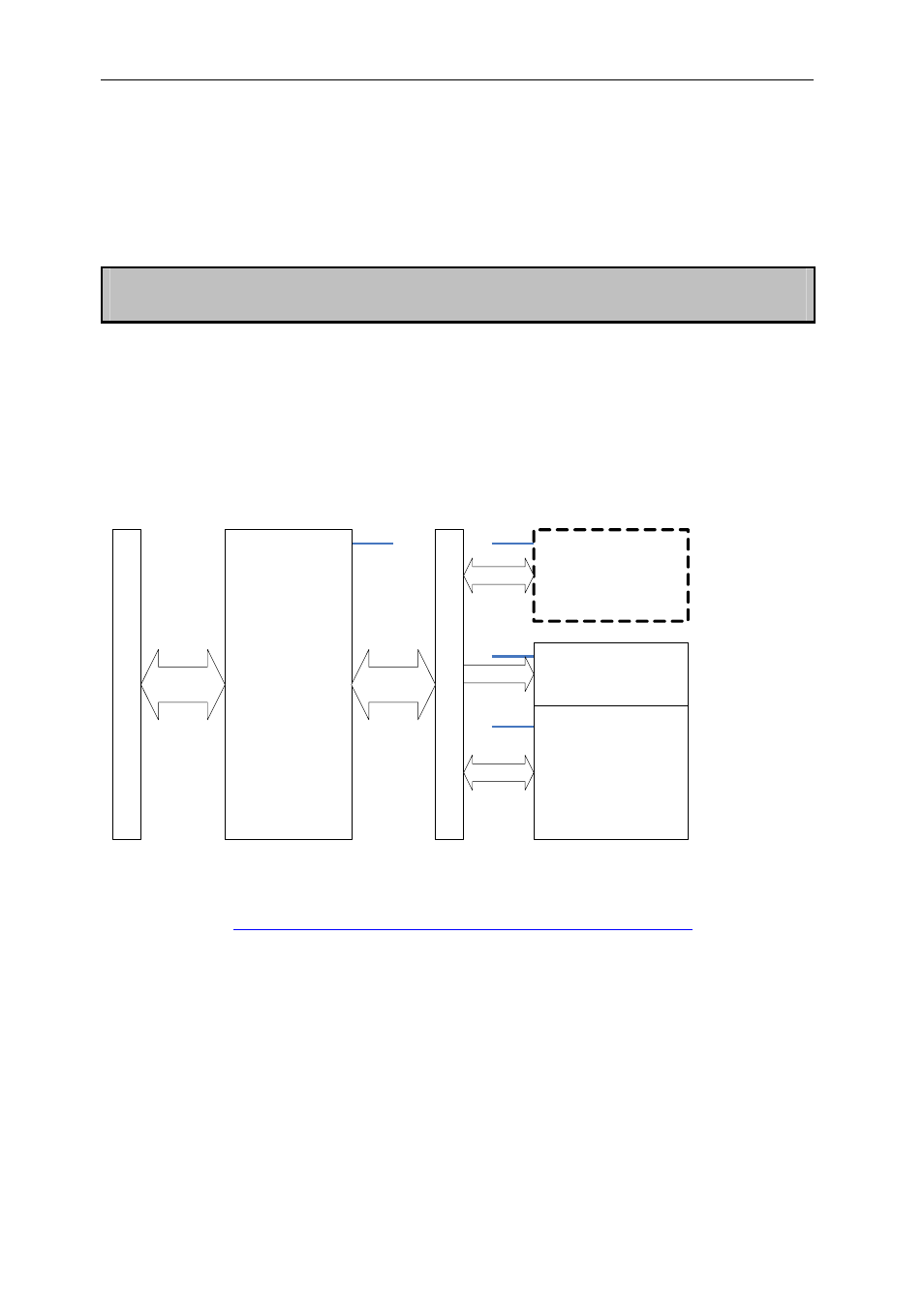

Page 11: Figure 3: ql5064 connection

Version 1.0.0

Page 11 of 38

SMT407 User Manual

QL5064

The QuickLogic PCI bridge is installed on all configurations of SMT407.

This device combines a 66MHz/64-bit PCI Master/Target ASIC core with a one-time

programmable (OTP) FPGA fabric.

The configuration of the FPGA fabric in the QL5064 is performed prior to

manufacturing of the module and can not be changed by the user.

Local bus

QL5064 provides a bridge between the PCI bus of the host system and the Local bus

of the SMT407. There are three primary functions of the Local bus on SMT407:

1) Configuration of the Virtex FPGA

2) Communication with logic designs loaded in the Virtex FPGA

3) Communication with DSPs over JTAG (applies to DSP boards only)

CS[3:0]

CS[1]

CS[0]

CS[3:2]

QL5064

Virtex FPGA design

Virtex FPGA config

TI JTAG controller

(DSP boards only)

8-bit

66MHz/

64-bit

PC

I b

u

s

L

o

cal

bu

s

16-bit

64-bit

50MHz/

64-bit

Figure 3: QL5064 connection

More information about the Local bus interface and protocols can be obtained from

QuickLogic at:

Virtex FPGA configuration

Programming of the Virtex FPGA can be achieved over the PCI bus using the

SelectMAP interface. This interface is 8-bits wide and runs at the full speed of the

Local bus. By simply writing a stream of configuration bytes to the location at CS[0]

the FPGA can be programmed.

An example of this is provided in the SMT6041-407 software package available from

SUNDANCE.