Westermo U200 Operator manal User Manual

Page 36

V4.5

www.westermo.com

U/R/T200 series

- 36 -

load dependable latency through off-the-shelf Ethernet switches without any time sync

support will depredate the time sync accuracy that can be achieved on the IEEE1588 Slaves.

This degradation is proportional with the number of off-the-shelf switches between the IEEE

1588 Grand Master and the IEEE 1588 Slave.

This problem is solved if T200 switches with IEEE 1588 Transparent Clock functionality are

used on all network paths between the Grand Masters and Slaves in the network.

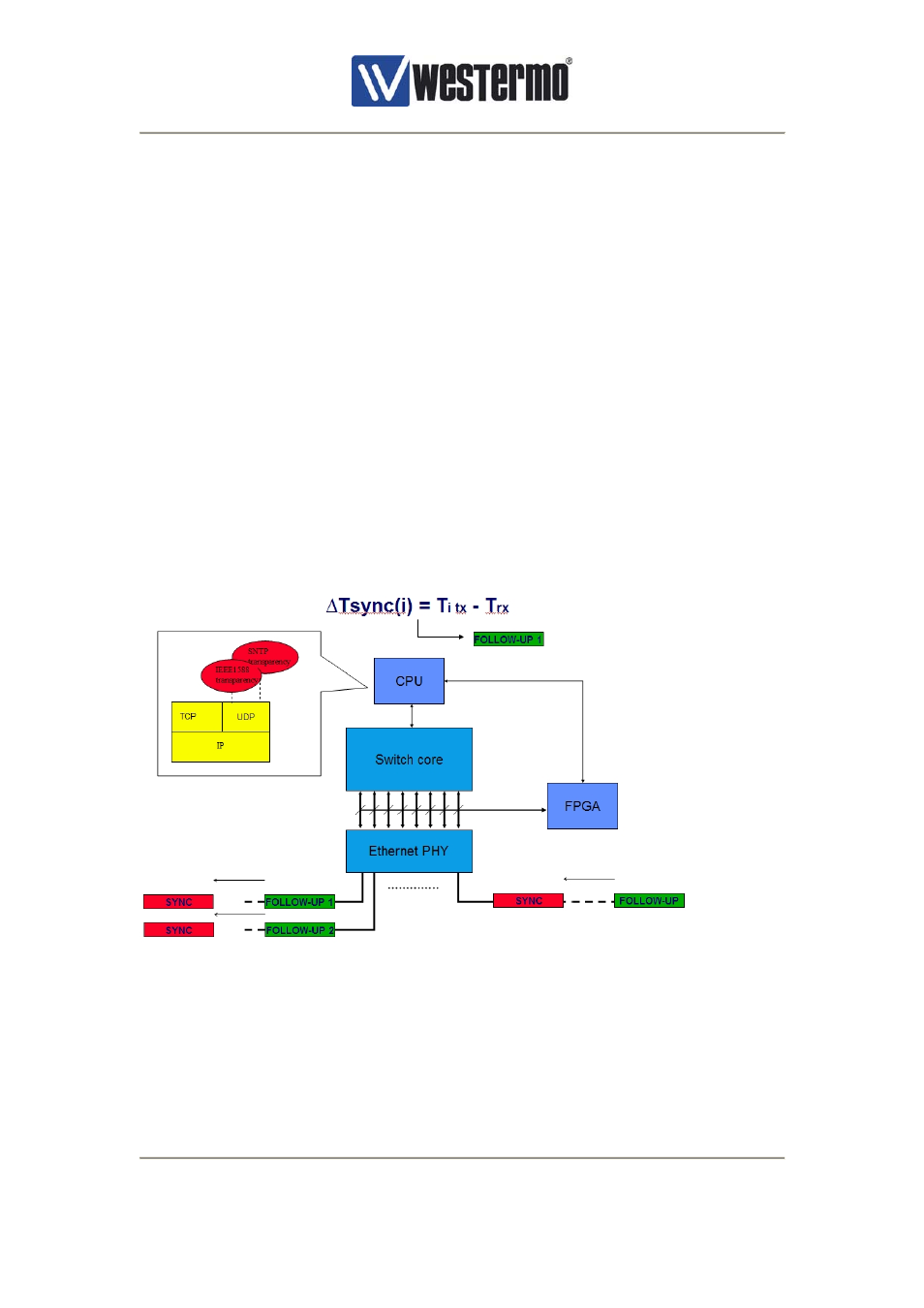

The IEEE 1588 Transparent Clock for IEEE1588 version 1 principles are as follows:

SYNC and FOLLOW_UP packets are sent from the Master to the Slaves. Both packets are

sent to the CPU of the Ethernet switch with Transparent Clock support before the packets are

forwarded on all ports except the port where the two packets were received. A receive time

stamp is generated on PHY level when the SYNC packet was received, and transmit time

stamps are generated on PHY level for each output port where the SYNC packets are

forwarded. The time difference between the transmit time stamps and the receive time

stamp, ∆Tsync(N-1) (,where N is the number of ports on the Ethernet switch), of the SYNC

packet is calculated and stored for each output port. The sequenceId of the SYNC packet is

also stored and compared with the assoiciatedSequenceId of the corresponding

FOLLOW_UP packet received on the same input port as the SYNC packet. These two

sequence ids must match. The preciseOriginTimestamp of each of the FOLLOW_UP packets

that are forwarded on the N-1 output ports are modified with ∆Tsync(i) for each output port.

The FOLLOW_UP packets are then forwarded on the output ports. See Figure 16 for the

handling of the SYNC/FOLLOW_UP packets at the switch with IEEE1588 Transparent Clock.

Figure 16, IEEE1588 SYNC/FOLLOW-UP Transparent Clock functionality

DEL_REQ packets are sent from the Slave to the Master in order to calculate the propagation

delay between Slave and the Master. This means the wire propagation delay in traditional

IEEE1588 context. The delay through an Ethernet switch with Transparent Clock support will

add network load depended switch delay to a DEL_REQ packet (i.e. store-and-forward and

queuing delays of the Ethernet switch). This delay must be removed. The delay is measured

when the DEL_REQ packet passes the switch and the delayReceiptTimestamp parameter of