Files generated by ip cores, Verilog hdl prototype location, Vhdl component declaration location – Altera MAX 10 Embedded Multipliers User Manual

Page 12: Files generated by ip cores -3

• Optionally select preset parameter values. Presets specify all initial parameter values for specific

applications (where provided).

• Specify parameters defining the IP core functionality, port configurations, and device-specific

features.

• Specify options for generation of a timing netlist, simulation model, testbench, or example design

(where applicable).

• Specify options for processing the IP core files in other EDA tools.

4. Click Finish or Generate to generate synthesis and other optional files matching your IP variation

specifications. The parameter editor generates the top-level

.qip

or

.qsys

IP variation file and HDL files

for synthesis and simulation. Some IP cores also simultaneously generate a testbench or example

design for hardware testing.

The top-level IP variation is added to the current Quartus II project. Click Project > Add/Remove Files

in Project to manually add a

.qip

or

.qsys

file to a project. Make appropriate pin assignments to connect

ports.

Files Generated by IP Cores

The following integer arithmetic IP cores use the MAX 10 device embedded multipliers block:

• LPM_MULT

• ALTMULT_ACCUM (MAC)

• ALTMULT_ADD

• ALTMULT_COMPLEX

Verilog HDL Prototype Location

You can view the Verilog HDL prototype for the IP cores in the following Verilog Design Files (.v):

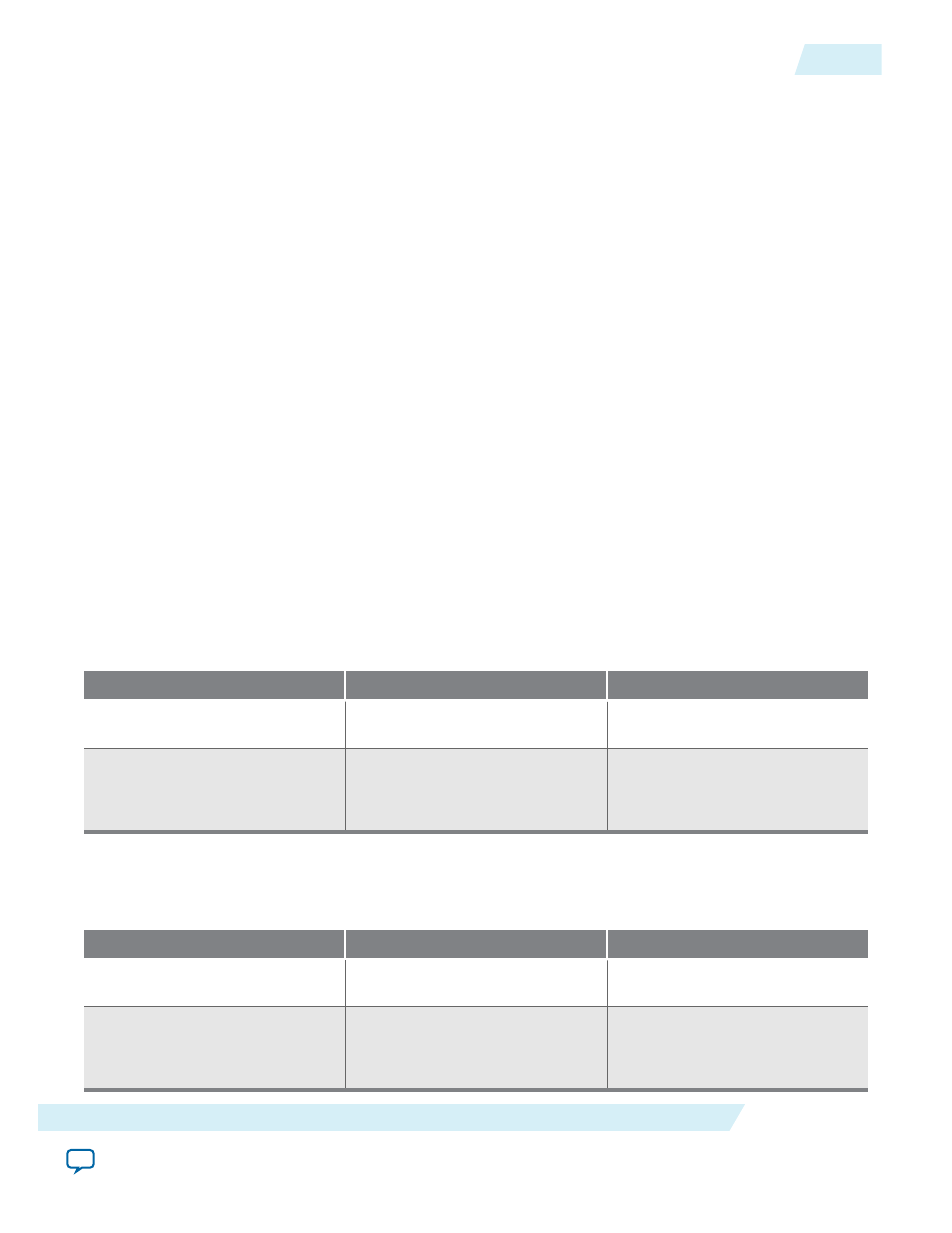

Table 3-1: Verilog HDL Prototype Location

Integer Arithmetic Megafunctions

Directory

Verilog Design File (.v)

LPM_MULT

<Quartus II installation directory>

\eda\synthesis

lpm.v

• ALTMULT_ACCUM

• ALTMULT_ADD

• ALTMULT_COMPLEX

<Quartus II installation directory>

\eda\synthesis

altera_mf.v

VHDL Component Declaration Location

You can view the VHDL component declaration for the IP cores in the following VHDL Design Files

(.vhd):

Integer Arithmetic Megafunctions

Directory

VHDL Design File (.vhd)

LPM_MULT

<Quartus II installation directory>

\libraries\vhdl\lpm

LPM_PACK.vhd

• ALTMULT_ACCUM

• ALTMULT_ADD

• ALTMULT_COMPLEX

<Quartus II installation directory>

\libraries\vhdl\altera_mf

altera_mf_components.vhd

UG-M10DSP

2014.09.22

Files Generated by IP Cores

3-3

Embedded Multipliers Implementation Guides

Altera Corporation