Altera MAX 10 Embedded Multipliers User Manual

Page 27

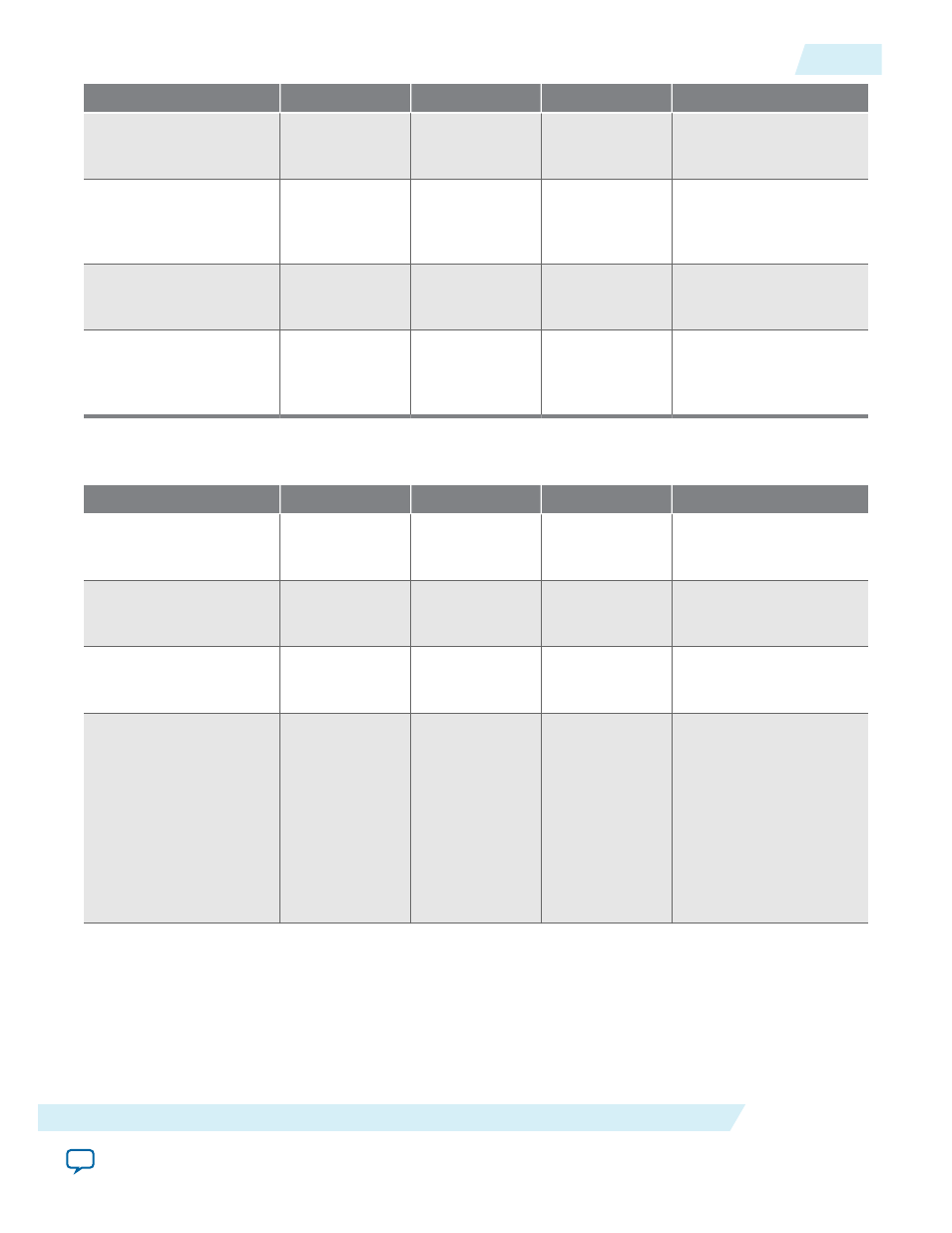

GUI Parameter

Parameter

Condition

Value

Description

Input Register > What

is the source for clock

input?

SIGNED_

REGISTER_B

Input

Representation >

More Options

Clock0–Clock3

Specifies the source for

clock input.

Input Register > What

is the source for

asynchronous clear

input?

SIGNED_

ACLR_B

Input

Representation >

More Options

• Aclr0–Aclr2

• None

Specifies the source for

asynchronous clear

input.

Pipeline Register >

What is the source for

clock input?

SIGNED_

PIPELINE_

REGISTER_B

Input

Representation >

More Options

Clock0–Clock3

Specifies the source for

clock input.

Pipeline Register >

What is the source for

asynchronous clear

input?

SIGNED_

PIPELINE_

ACLR_B

Input

Representation >

More Options

• Aclr0–Aclr2

• None

Specifies the source for

asynchronous clear

input.

Table 6-2: ALTMULT_ADD Parameters - Extra Modes

This table lists the IP core parameters applicable to MAX 10 devices.

GUI Parameter

Parameter

Condition

Value

Description

Create a shiftout

output from A input of

the last multiplier

—

—

On or Off

Turn on to create a

signal from A input.

Create a shiftout

output from B input of

the last multiplier

—

—

On or Off

Turn on to create a

signal from B input.

Register output of the

adder unit

—

—

On or Off

Turn on to create a

register output of the

adder unit.

What is the source for

clock input?

OUTPUT_

REGISTER

• Outputs

Configuration

> Register

output of the

adder unit =

On

• Outputs

Configuration

> More

Options

Clock0–Clock3

Specifies the clock

signal for the output

register.

UG-M10DSP

2014.09.22

ALTMULT_ADD Parameter Settings

6-3

ALTMULT_ADD (Multiply-Adder) IP Core References

Altera Corporation