Multiplier stage, Output register, Multiplier stage -2 – Altera MAX 10 Embedded Multipliers User Manual

Page 6: Output register -2

• An input register

• The multiplier in 9- or 18-bit sections

Each multiplier input signal can be sent through a register independently of other input signals. For

example, you can send the multiplier

Data A

signal through a register and send the

Data B

signal directly

to the multiplier.

The following control signals are available to each input register in the embedded multiplier:

• Clock

• Clock enable

• Asynchronous clear

All input and output registers in a single embedded multiplier are fed by the same clock, clock enable, and

asynchronous clear signals.

Multiplier Stage

The multiplier stage of an embedded multiplier block supports 9 × 9 or 18 × 18 multipliers and other

multipliers in between these configurations. Depending on the data width or operational mode of the

multiplier, a single embedded multiplier can perform one or two multiplications in parallel.

Each multiplier operand is a unique signed or unsigned number. Two signals,

signa

and

signb

, control

an input of a multiplier and determine if the value is signed or unsigned. If the

signa

signal is high, the

Data A

operand is a signed number. If the

signa

signal is low, the

Data A

operand is an unsigned

number.

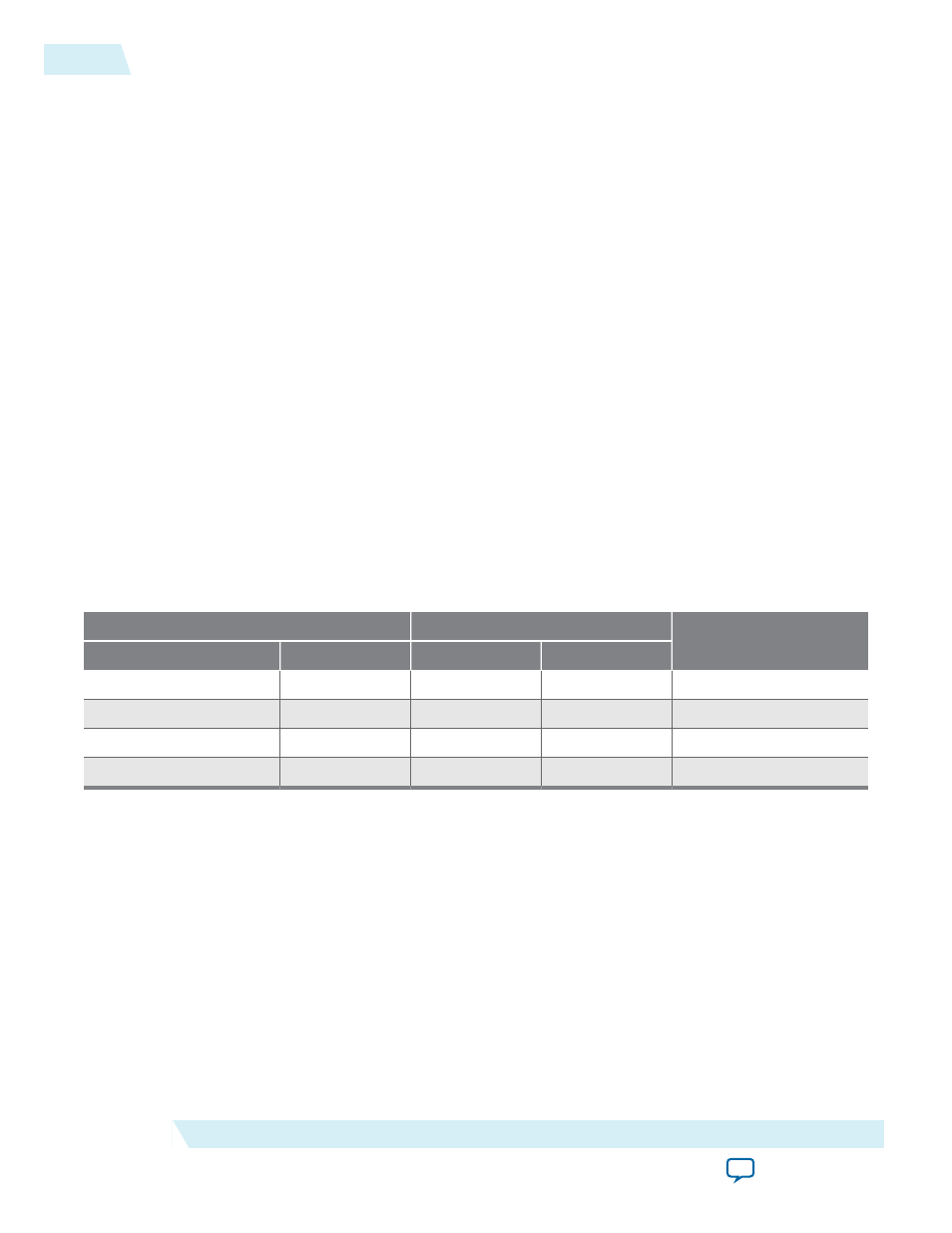

The following table lists the sign of the multiplication results for the various operand sign representations.

The results of the multiplication are signed if any one of the operands is a signed value.

Data A

Data B

Result

signa

Value

Logic Level

signb

Value

Logic Level

Unsigned

Low

Unsigned

Low

Unsigned

Unsigned

Low

Signed

High

Signed

Signed

High

Unsigned

Low

Signed

Signed

High

Signed

High

Signed

You can dynamically change the

signa

and

signb

signals to modify the sign representation of the input

operands at run time. You can send the

signa

and

signb

signals through a dedicated input register. The

multiplier offers full precision, regardless of the sign representation.

When the

signa

and

signb

signals are unused, the Quartus II software sets the multiplier to perform

unsigned multiplication by default.

Output Register

You can register the embedded multiplier output using output registers in either 18- or 36-bit sections.

This depends on the operational mode of the multiplier. The following control signals are available for

each output register in the embedded multiplier:

2-2

Multiplier Stage

UG-M10DSP

2014.09.22

Altera Corporation

Embedded Multipliers Features and Architecture