Altera MAX 10 Embedded Multipliers User Manual

Page 22

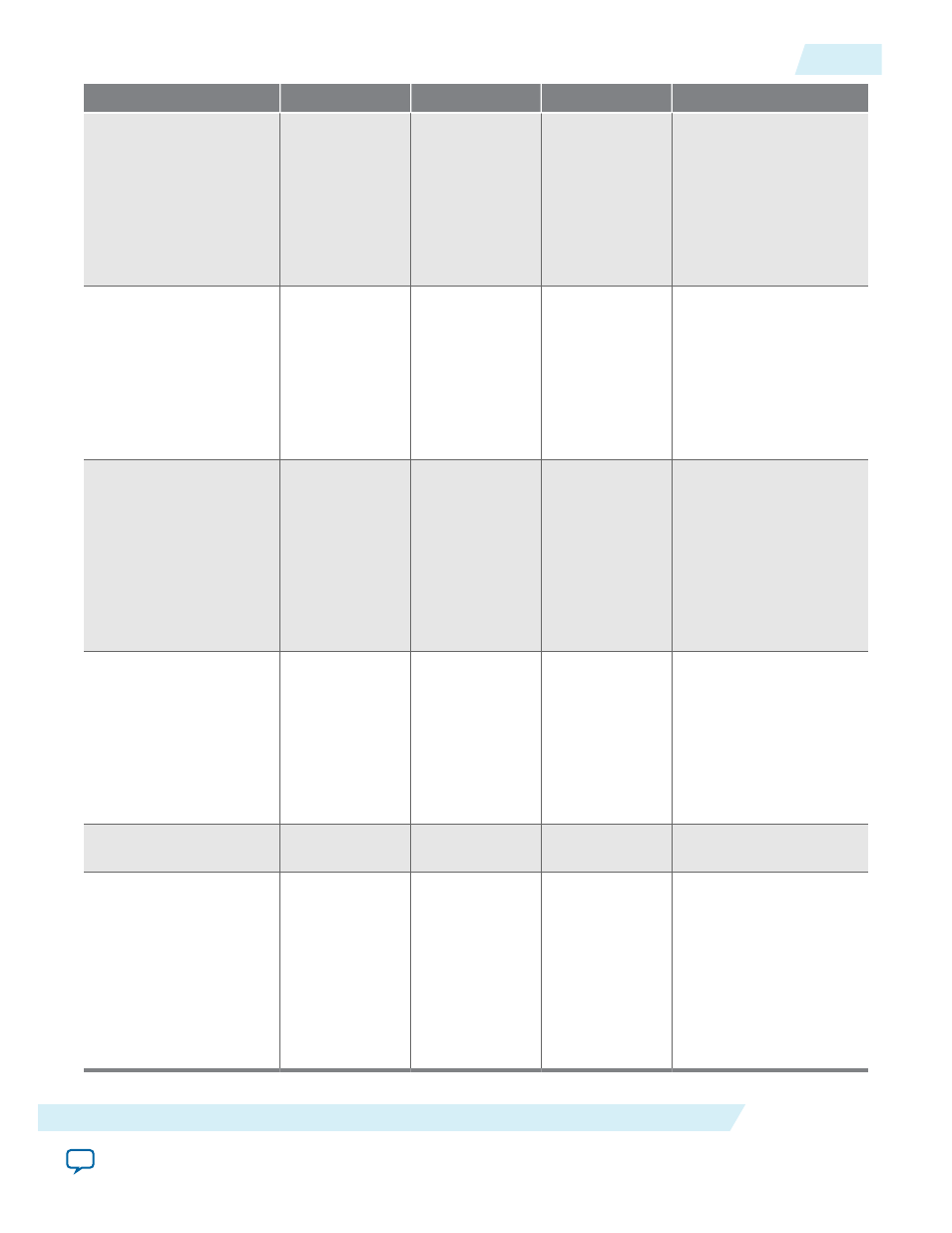

GUI Parameter

Parameter

Condition

Value

Description

Input Register > What

is the source for clock

input?

ACCUM_

SLOAD_REG

• Accumulator

> Create an

‘accum_sload’

input port =

On

• Accumulator

> More

Options

Clock0–Clock3

Specifies the clock

signal for the

accum_

sload

port.

Input Register > What

is the source for

asynchronous clear

input?

ACCUM_

SLOAD_ACLR

• Accumulator

> Create an

‘

accum_

sload

’ input

port = On

• Accumulator

> More

Options

• Aclr0–Aclr2

• None

Specifies the asynchro‐

nous clear source for

the first register on the

accum_sload

input.

Pipeline Register >

What is the source for

clock input?

ACCUM_

SLOAD_

PIPELINE_REG

• •

Accumulator

> Create an

‘

accum_

sload

’ input

port = On

• Accumulator

> More

Options

Clock0–Clock3

Specifies the source for

clock input.

Pipeline Register >

What is the source for

asynchronous clear

input?

ACCUM_

SLOAD_

PIPELINE_

ACLR

• Accumulator

> Create an

‘

accum_soad

’

input port =

On

• Accumulator

> More

Options

• Aclr0–Aclr2

• None

Specifies the source for

asynchronous clear

input.

Create an ‘

overflow

’

output port

—

—

On or Off

Overflow

port for the

accumulator

Add [] extra latency to

the multiplier output

EXTRA_

MULTIPLIER_

LATENCY

—

0, 1, 2, 3, 4, 5, 6,

7, 8, or 12

Specifies the number of

clock cycles of latency

for the multiplier

portion of the DSP

block. If the

MULTIPLIER_REG

parameter is specified,

then the specified clock

port is used to add the

latency.

UG-M10DSP

2014.09.22

ALTMULT_ACCUM Parameter Settings

5-7

ALTMULT_ACCUM (Multiply-Accumulate) IP Core References

Altera Corporation