Altera RAM Initializer User Manual

Page 30

2–18

Confidential—Internal Use Only

Altera Corporation

RAM Initializer (ALTMEM_INIT) Megafunction User Guide

May 2008

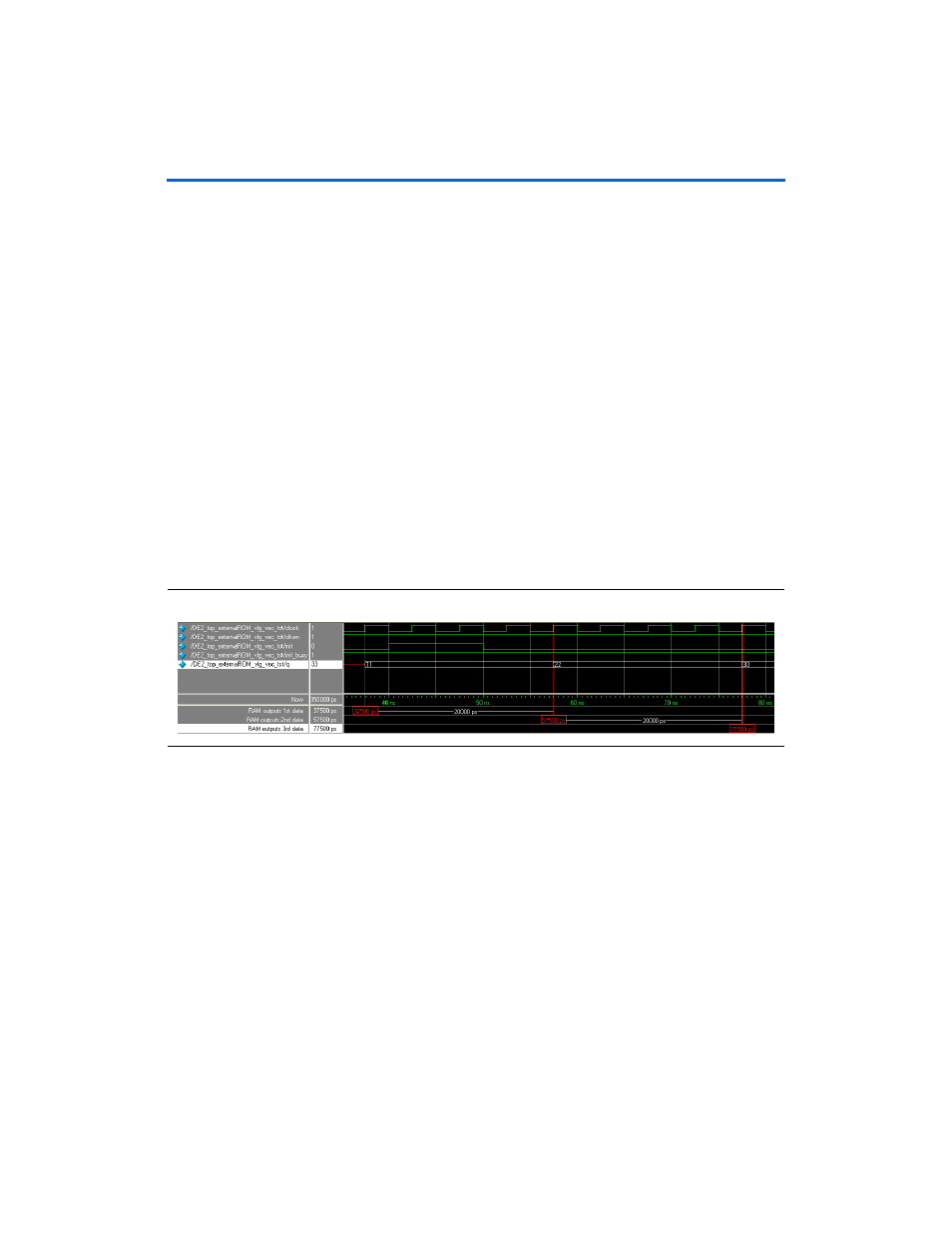

Design Example 2: Memory Initialization with External ROM

At the second rising edge of the clock at 12,500 ps, the ALTMEM_INIT

megafunction initiates a read from the ROM. Both the address input port

and data output port of the external on-chip ROM are registered;

therefore, the value of the ROM_READ_LATENCY parameter is set to 2.

With this setting, the ALTMEM_INIT megafunction waits 2 clock cycles,

from 12,500 ps to 22,500 ps, before sampling data at the next rising edge

of the clock at 27,500 ps.

1

If the ROM does not have any registered output ports, set the

ROM_READ_LATENCY

parameter to 1.

As both the input and output ports of the RAM are also registered, there

is a delay of another 2 clock cycles before the value appears at the output

port of the RAM at 37,500 ps.

In total, upon assertion of the init signal, the first value is delayed by

6 clock cycles before showing up at the output port of the RAM.

shows the delay cycles of the first value and subsequent

values that appear at the RAM output port after the init signal is

asserted.

Figure 2–15. Design Example 2: Delay Cycles of First Value and Subsequent Values at the RAM Output Port

, the RAM sends the first value, 0x11, to its output port

after 6 clock cycles. The subsequent values, 0x22 and 0x33, are delayed by

4 clock cycles—2 clock cycles for the ROM read latency and another

2 clock cycles for the value to appear at the output port of the RAM.

Therefore, if your design or application needs to read from the RAM

without waiting for the initialization process to complete, you can read

the first and subsequent values by taking these delays into consideration.

In this design example, for example, you can read the first value at the

seventh clock cycle after the init signal is asserted. After that, you can

read the subsequent values at intervals of 4 clock cycles.