Generate files, Generate files –5 – Altera CRC Compiler User Manual

Page 15

Chapter 2: Getting Started

2–5

CRC Compiler Walkthrough

© November 2009

Altera Corporation

Preliminary

You can click Back to display the previous page or click Parameter Setting, EDA or

Summary

, if you want to change any of the MegaWizard options.

Generate Files

To generate the files, follow these steps:

1. Turn on the files you wish to generate.

1

At this stage you can still click Back or the pages to display any of the other

pages in the MegaWizard interface, if you want to change any of the

parameters.

2. To generate the specified files and close the MegaWizard interface, click Finish.

The Generation Status Window appears. After file generation is successful, click

Exit

to close the window.

1

The generation phase may take several minutes to complete. The

generation status window tells you the files that are generated and reports

whether the generation phase was successful or not.

3. After you review the generation report, click Exit to close the MegaWizard Plug-In

Manager and click Yes on the Quartus II IP Files message.

1

The Quartus II IP File (.qip) is a file generated by the MegaWizard interface

or SOPC Builder that contains information about a generated IP core. You

are prompted to add this .qip file to the current Quartus II project at the

time of file generation. In most cases, the .qip file contains all of the

necessary assignments and information required to process the core or

system in the Quartus II compiler. Generally, a single .qip file is generated

for each MegaCore function and for each SOPC Builder system. However,

some more complex SOPC Builder components generate a separate .qip

file, so the system .qip file references the component .qip file.

describes the generated files and other files that may be in your project

directory. The names and types of files specified in the summary vary based on

whether you created your design with VHDL or Verilog HDL.

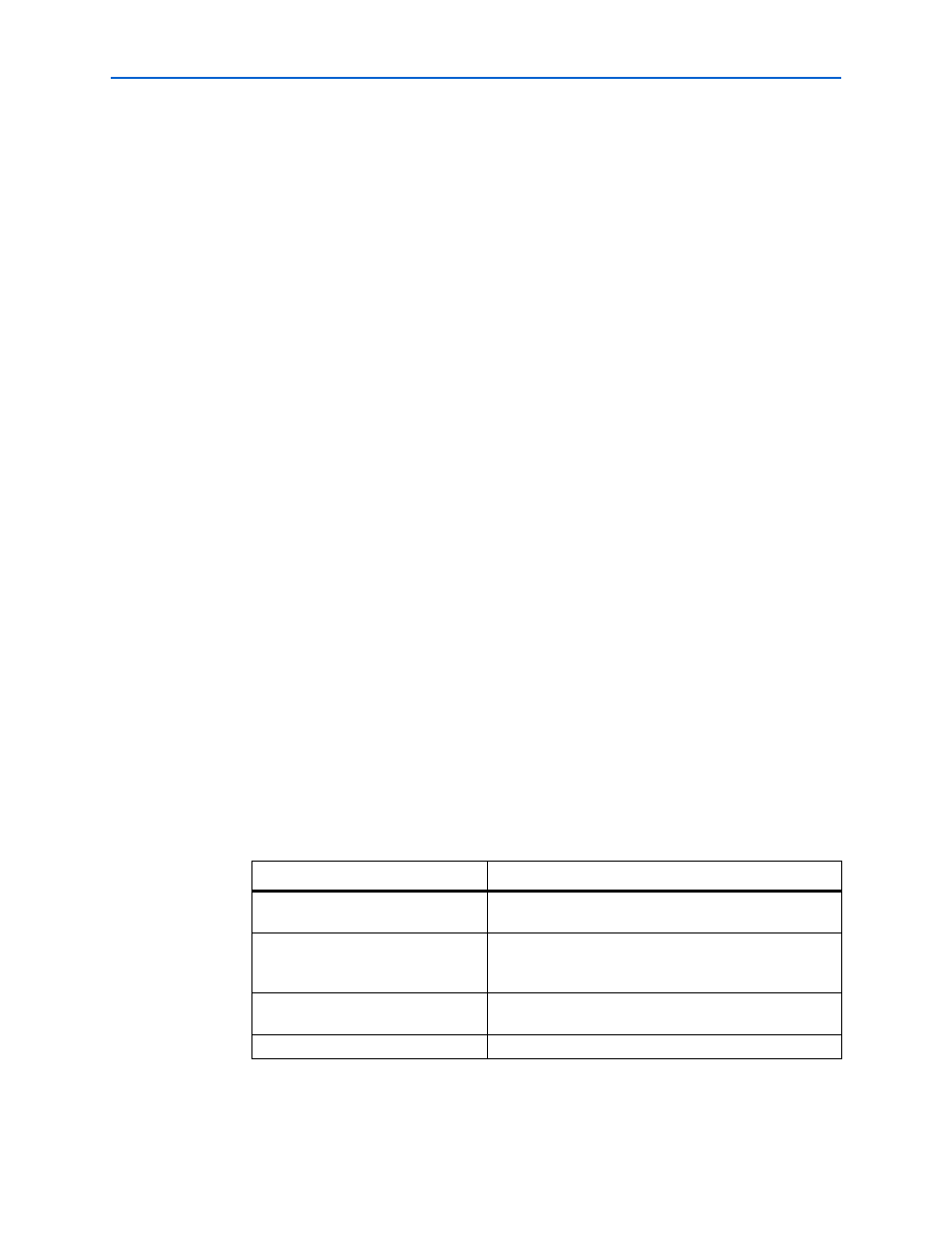

Table 2–1. Generated Files (Sheet 1 of 2)

File Name

Description

<variation name>.bsf

Quartus II symbol file for the MegaCore function variation.

You can use this file in the Quartus II block diagram editor.

<variation name>.cmp

A VHDL component declaration file for the MegaCore

function variation. Add the contents of this file to any VHDL

architecture that instantiates the MegaCore function.

<variation name>.html

Report file which contains lists of the generated files and

ports for the MegaCore function variation.

<variation name>.vo or .vho

VHDL or Verilog HDL IP functional simulation model.