Simulate the design, Compile the design, Program a device – Altera CRC Compiler User Manual

Page 16

2–6

Chapter 2: Getting Started

Simulate the Design

© November 2009

Altera Corporation

Preliminary

You can now integrate your custom MegaCore function variation into your design,

simulate, and compile your design.

Simulate the Design

You can simulate your design using the MegaWizard-generated VHDL or Verilog

HDL IP functional simulation models. These simulation models are generated in the

language you selected in

“Set Up Simulation” on page 2–4

For an example of simulating a design, refer to the section,

f

For more information on IP functional simulation models, re

er in volume 3 of the Quartus II

Handbook.

Compile the Design

You can use the Quartus II software to compile your design. Refer to Quartus II Help

for instructions on compiling your design.

Program a Device

After you compile your design, program your targeted Altera device

and verify your

design in hardware.

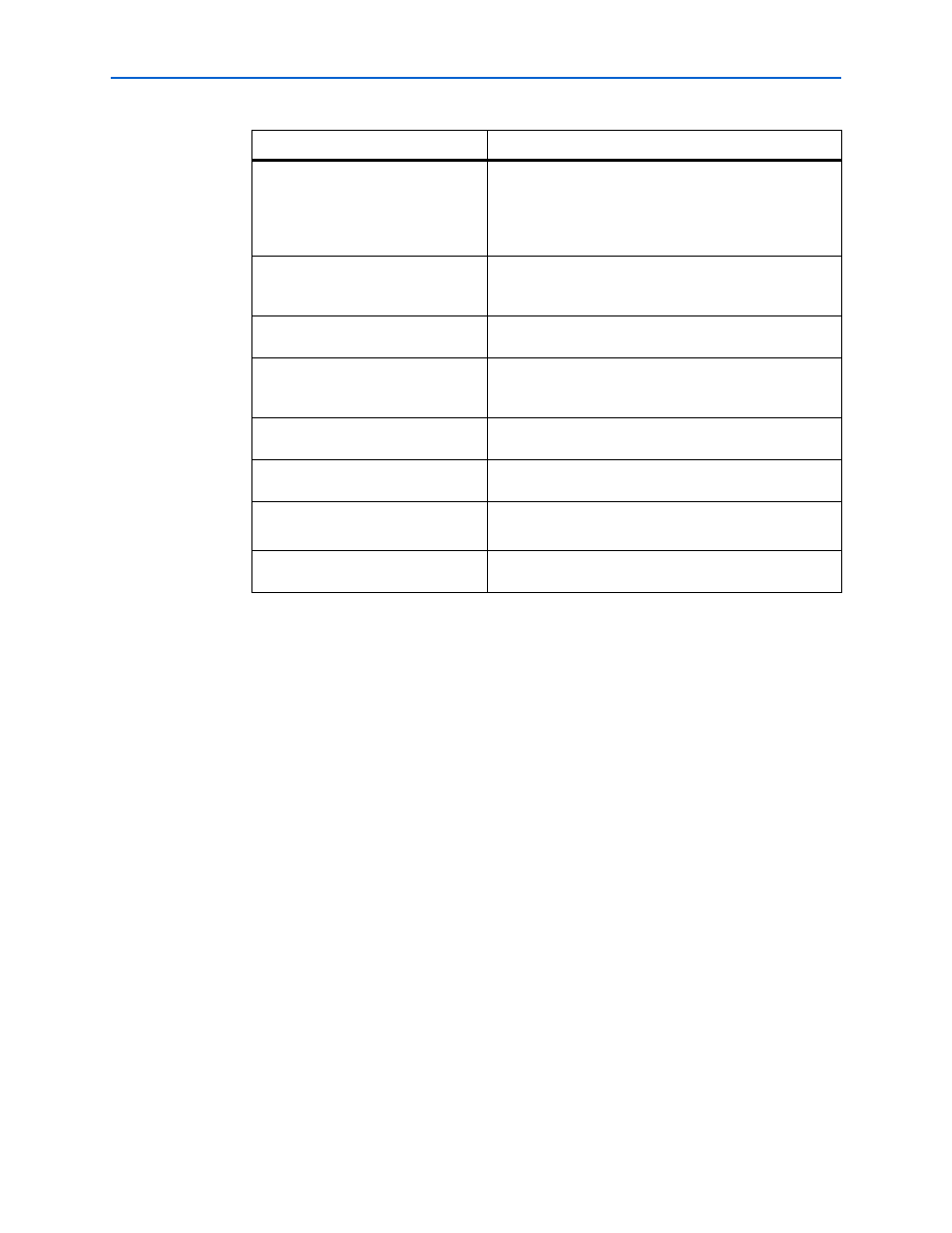

<variation name>.vhd or .v

A MegaCore function variation file, which defines a VHDL

or Verilog HDL top-level description of the custom

MegaCore function. Instantiate the entity defined by this

file inside of your design. Include this file when compiling

your design in the Quartus II software.

<variation name>_bb.v

Verilog HDL black-box file for the MegaCore function

variation. Use this file when using a third-party EDA tool to

synthesize your design.

<variation name>.qip

Contains Quartus II project information for your MegaCore

function variations.

<variation name>_syn.v

A timing and resource estimation netlist for use in some

third-party synthesis tools. This file is generated when the

option Generate netlist on the EDA page is turned on.

testbench/tb.v(hd) or

testbench/tb_multichan.v(hd)

A Verilog or VHDL testbench file that provides a testbench

for the CRC compiler MegaCore function variation.

testbench/crcdemo.v(hd) or

testbench/crcdemo_multichan.v(hd)

A Verilog or VHDL example design incorporating a CRC

generator, checker, and other supporting models.

testbench/crcgen.v(hd) or

testbench/crcgen_multichan.v(hd)

Wrapper for example variations of the CRC Compiler

MegaCore function used in the testbench.

testbench/crcchk.v(hd) or

testbench/crcchk_multichan.v(hd)

Wrapper for example variations of the CRC Compiler

MegaCore function used in the testbench.

Table 2–1. Generated Files (Sheet 2 of 2)

File Name

Description