Multi-channel operation, Multi-channel operation –4 – Altera CRC Compiler User Manual

Page 20

3–4

Chapter 3: Functional Description

Multi-Channel Operation

© November 2009

Altera Corporation

Preliminary

Multi-Channel Operation

For multi-channel (Number of CRC Channels > 1) operations, the CRC Compiler

inserts context memories which allow a generator or checker to process multiple

packets concurrently. Both speed and area optimization variants support multi-

channel operation.

On each

datavalid

cycle, user applications must set the

datachannel

input signal

to the channel context in use. The MegaCore function sets the

crcchannel

output

signal to the same value after a fixed number of clock latency (at the assertion of

crcvalid

), to indicate the channel the

crcbad

or

checksum

output signal applies

to.

There is no channel switch latency or minimum number of cycles between context

switches, and no restriction on channel ordering is imposed. The latency of a multi-

channel MegaCore function is identical to that of the corresponding single-channel

MegaCore function.

However, there is an fmax penalty in multi-channel operation. After each system reset

(

reset_n

= 0), there will be a slight delay in terms of the number of clock cycles due

to an internal initialization of the context to a known state. The

chaninitdone

output signal is asserted when the internal initialization is done. You must wait until

this output signal is asserted before sending any data to the MegaCore function for

processing.

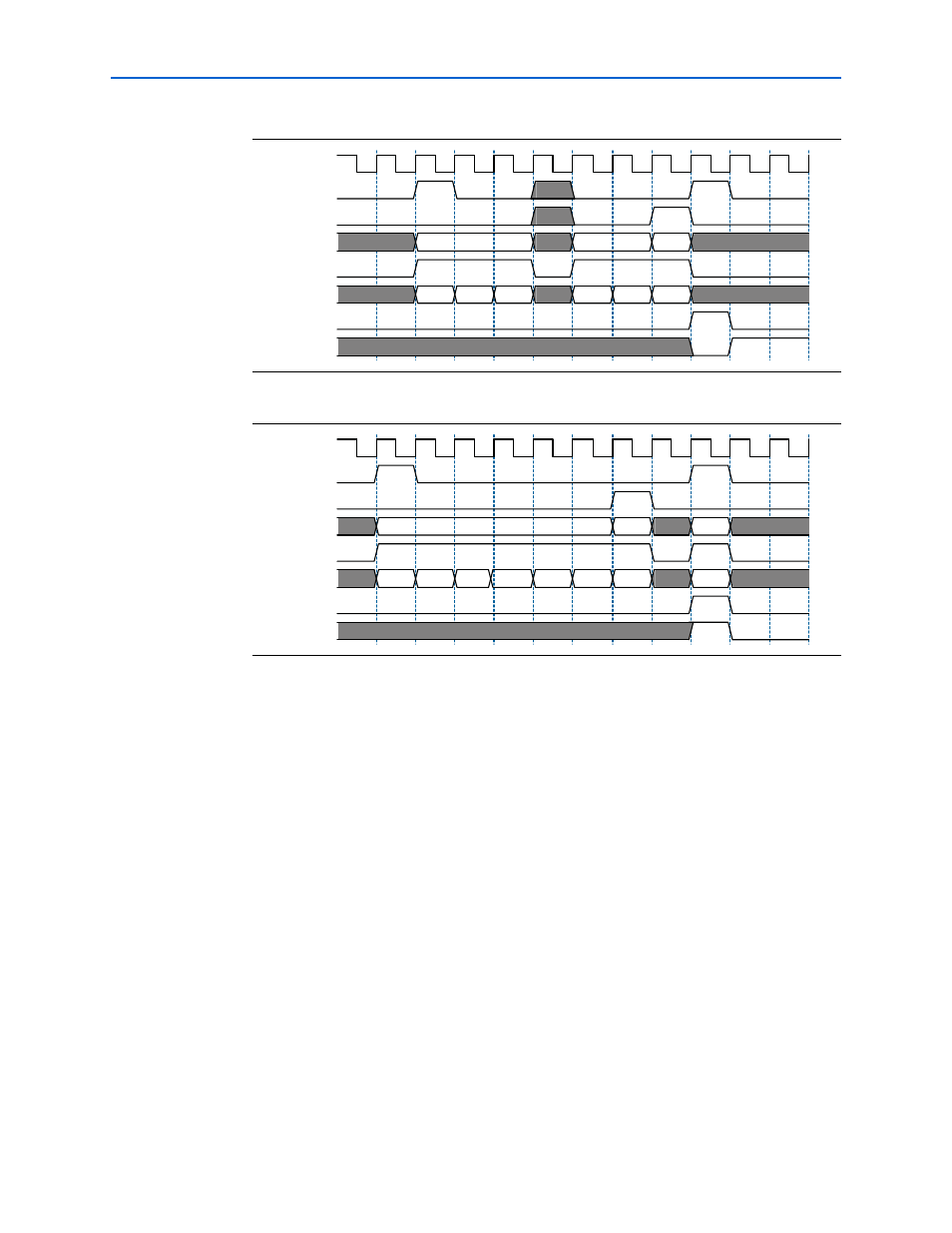

Figure 3–6. Checker Operation With Good Codeword

Figure 3–7. Checker Operation With Bad Codeword

clk

startofpacket

endofpacket

empty[3:0]

datavalid

data[7:0]

crcvalid

crcbad

0

0

n

data1

data2

data3

data4

data5

checksum

clk

startofpacket

endofpacket

empty[3:0]

datavalid

data[7:0]

crcvalid

crcbad

0

n

0

data1

data2

data3

data4

data5

data6

checksum

data1