Running the testbench example, Running the testbench example –8, Running the testbench – Altera CRC Compiler User Manual

Page 24: N in, Figure 3–11

3–8

Chapter 3: Functional Description

Running the Testbench Example

© November 2009

Altera Corporation

Preliminary

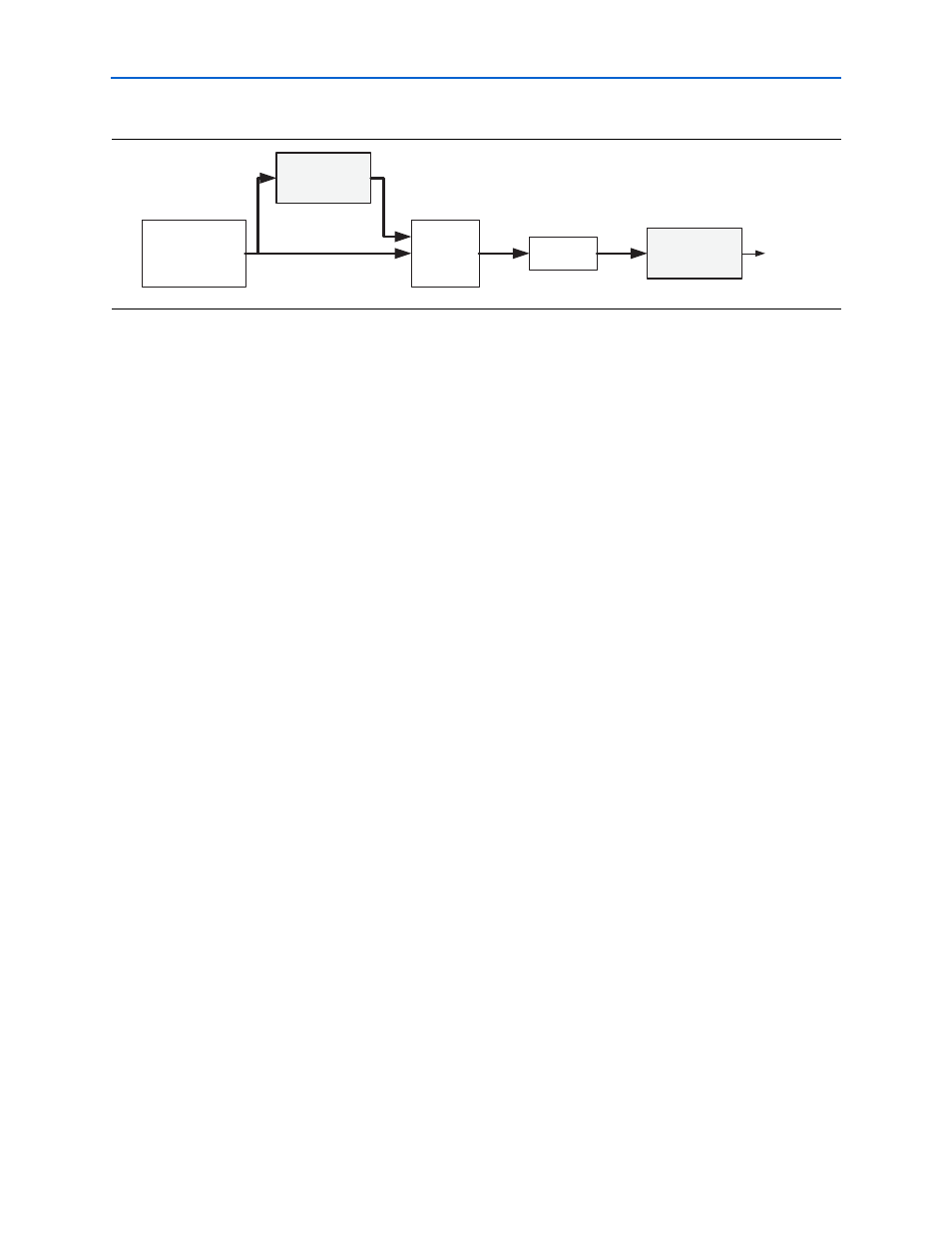

The packet generator module creates sample message words (packets without CRCs).

The CRC generator creates a

checksum

, which the merge module appends to the end

of the packet. The merge module delays the data to account for generator processing

time. The result is a codeword. The channel module inserts errors in the codewords,

as indicated by the

errorInserted

signal. The CRC checker indicates the presence

of errors in the received codewords. The testbench shows detected errors using the

errorDetected

signal.

Running the Testbench Example

In this section you run the testbench example to illustrate how you do the following

tasks:

■

Create a testbench project using the Quartus II New Project Wizard

■

Create simulation models for the generator and checker using the MegaWizard

interface

■

Set EDA Tool Settings to simulate your testbench project

■

Run compilation and analysis

When you create a MegaCore function variation and turn on the Generate

Simulation Model

option on the EDA page, the Quartus II software generates the

simulation model in the project directory. The simulation model is an Intellectual

Property Functional Simulation (IPFS) model with a file extension of .vo or .vho,

depending on the language you select. It also creates an example design in the

testbench

subdirectory. The testbench subdirectory contains the data generator,

merge, and channel modules for the example testbench in the following files:

■

A top-level simulation file, tb.v or tb.vhd.

■

crcdemo.v(hd)

for a single channel MegaCore function or

crcdemo_multichan.v(hd)

for a multichannel MegaCore function

■

A generator variation file, crcgen.v(hd) for a single channel MegaCore function or

crcgen_multichan.v(hd)

for a multichannel MegaCore function.

■

The corresponding checker variation file, crcchk.v(hd) for a single channel

MegaCore or crcchk_multichan.v(hd) for a multichannel MegaCore.

Figure 3–11. Testbench Architecture

Data generator

CRC

Generator

Merge

Channel

CRC checker

Error

status

Codeword

Codeword

+ errors

Message

word