Altera CRC Compiler User Manual

Page 18

3–2

Chapter 3: Functional Description

CRC Generator

© November 2009

Altera Corporation

Preliminary

empty

are ignored. Following a fixed number of clock cycles after the final word,

indicated by assertion of

endofpacket

,

crcvalid

is asserted and the computed

CRC value is available on the

checksum

output. The value of

checksum

is

undefined at other times. For the delay between assertion of

endofpacket

and

crcvalid

, refer to the Latency panel of the MegaWizard interface.

The CRC generator can start computing the checksum of a new packet while it is

completing the calculation for the previous packet, that is before it asserts

crcvalid

.

The data source may assert

startofpacket

on the clock cycle immediately

following

endofpacke

t, regardless of the generator's latency.

shows a typical application of the CRC Generator and

operations respectively.

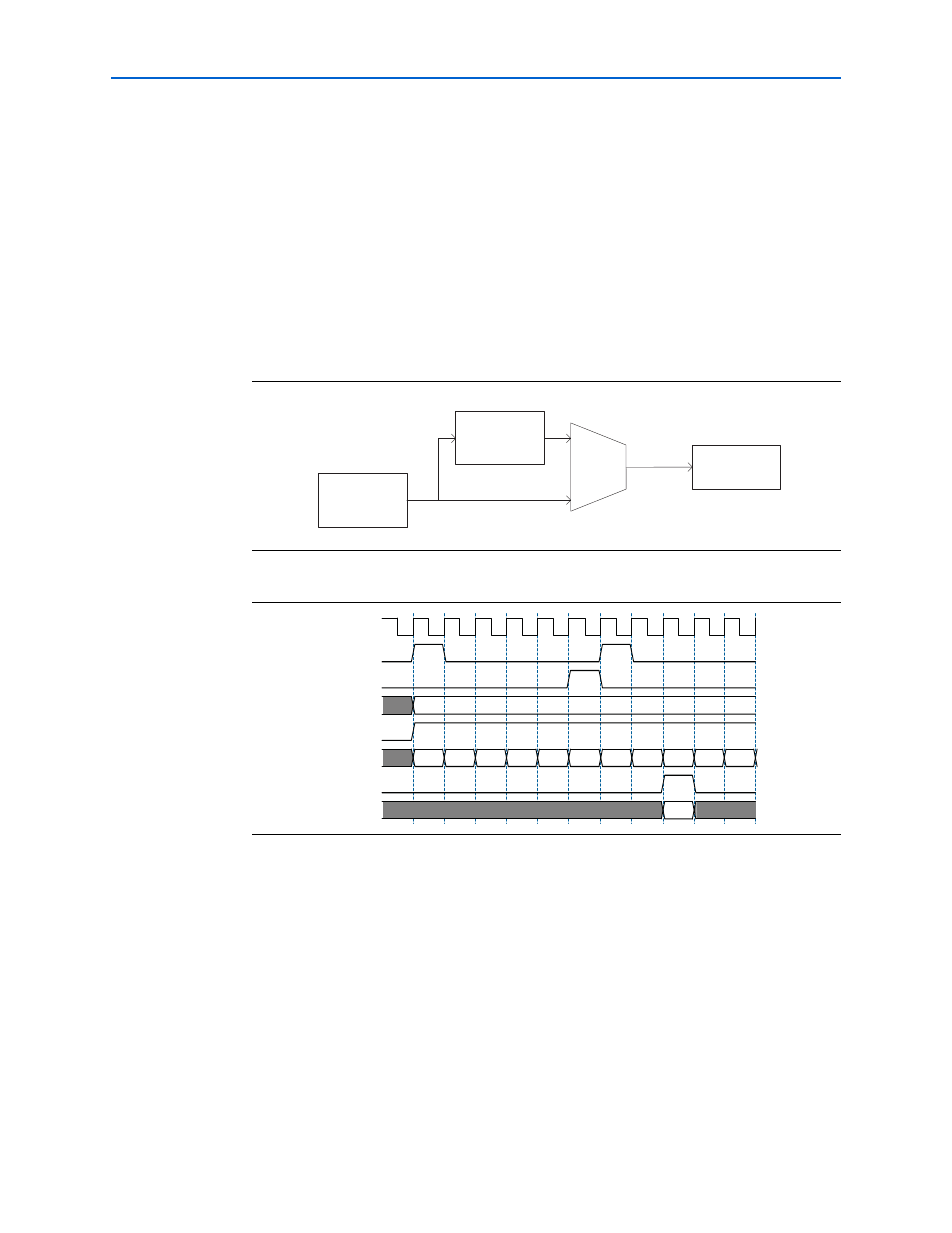

Figure 3–2. Typical CRC Generator Application

Figure 3–3. CRC Generator Operation

Data source

CRC

Generator

Merge

Message bits

Codeword

bits

Transmitter

clk

startofpacket

endofpacket

empty[3:0]

datavalid

data[7:0]

crcvalid

checksum[7:0]

0

data1

data2

data3

data4

data5

data6

data1

data2

data3

data4

data5

checksum