Multichannel ncos, Frequency hopping, Multichannel ncos -5 – Altera NCO MegaCore Function User Manual

Page 22: Frequency hopping -5

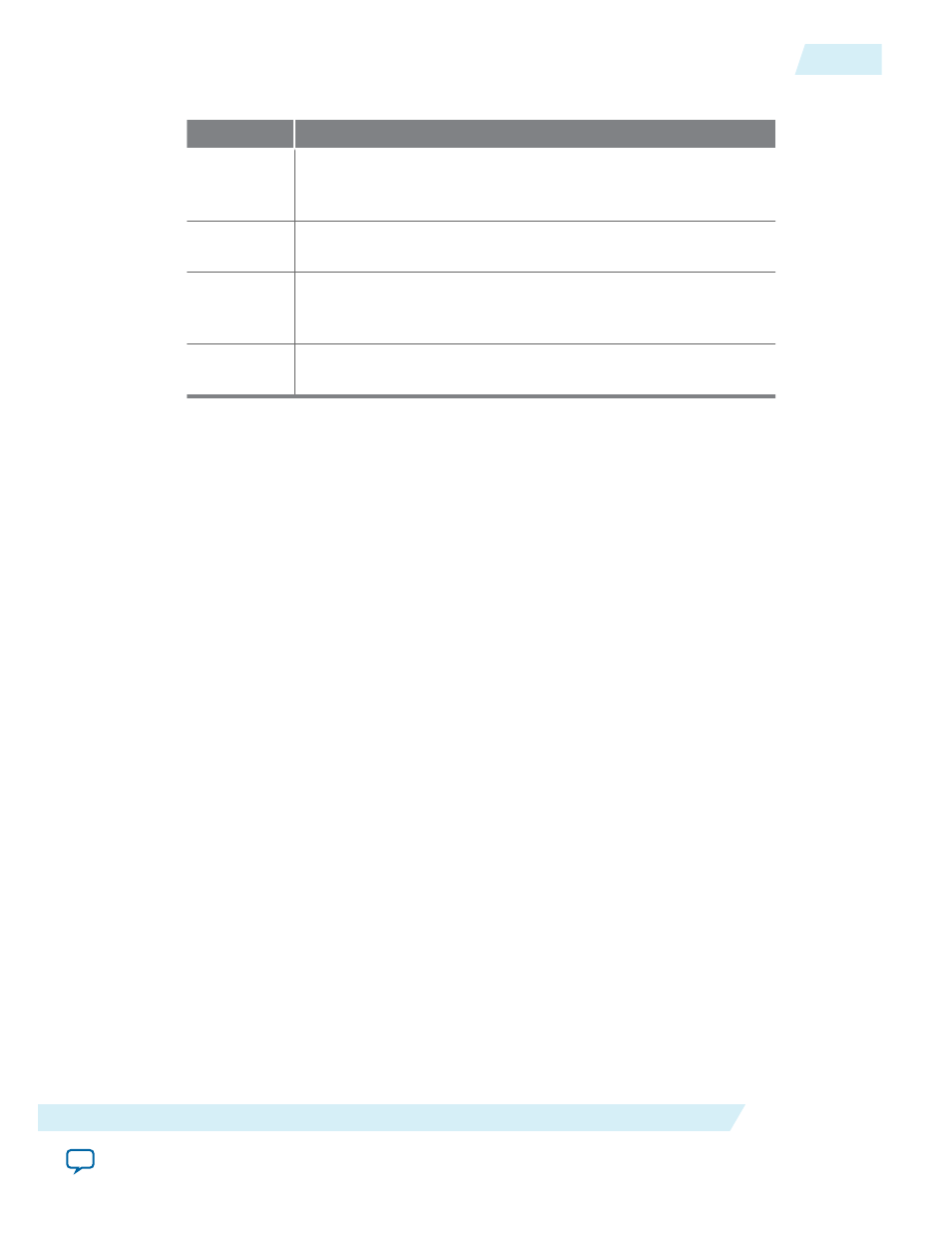

Table 3-2: Architecture Comparison

Architecture

Advantages

Large

ROM

Good for high speed and when a large quantity of internal

memory is available. Gives the highest spectral purity and uses

the fewest logic elements for a given parameterization.

Small

ROM

Good for high output frequencies with reduced internal memory

usage when a lower SFDR is acceptable.

CORDIC High performance solution when internal memory is at a

premium. The serial CORDIC architecture uses fewer resources

than parallel although the throughput is reduced.

Multiplier

-Based

Reduced memory usage by implementing multipliers in logic

elements or dedicated circuitry.

Multichannel NCOs

The NCO IP core allows you to implement multichannel NCOs. You can generate multiple sinusoids of

independent frequency and phase t at a very low cost in additional resources. The waveforms have an

output sample-rate of f

clk

/M where M is the number of channels. You can select 1 to 8 channels.

Multichannel implementations are available for all single-cycle generation algorithms. The input phase

increment, frequency modulation value and phase modulation input are input sequentially to the NCO

with the input values corresponding to channel 0 first and channel (M–1) last. The inputs to channel 0

should be input on the rising clock edge immediately following the de-assertion of the NCO reset.

On the output side, the first output sample for channel 0 is output concurrent with the assertion of

out_valid

and the remaining outputs for channels 1 to (M–1) are output sequentially.

If you select a multichannel implementation, the NCO MegaCore function generates VHDL and Verilog

HDL testbenches that time-division-multiplex the inputs into a single stream and demultiplex the output

streams into their respective downsampled channelized outputs.

Related Information

NCO Multichannel Design Example

on page 4-1

Frequency Hopping

The NCO IP core supports frequency hopping (except the serial CORDIC architecture). Frequency

hopping allows control and configuration of the NCO IP core at run time so that carriers with different

frequencies can be generated and held for a specified period of time at specified slot intervals.

The IP core supports multiple phase increment registers that you can load using an Avalon-MM bus. You

select the phase increment register using an external hardware signal; changes on this signal take effect on

the next clock cycle. The maximum number of phase increment registers is 16.

Note: During frequency hopping, the phase of the carrier should not experience discontinuous change.

Discontinuous carrier phase changes may cause spectral emission problems.

UG-NCO

2014.12.15

Multichannel NCOs

3-5

NCO IP Core Functional Description

Altera Corporation