Nco ip core signals, Nco ip core signals -10 – Altera NCO MegaCore Function User Manual

Page 27

and valid signals. Avalon-ST interfaces can also support more complex protocols for burst and packet

transfers with packets interleaved across multiple channels. The Avalon-ST interface inherently synchro‐

nizes multichannel designs, which allows you to achieve efficient, time-multiplexed implementations

without having to implement complex control logic.

Avalon-ST interfaces support backpressure, which is a flow control mechanism where a sink can signal to

a source to stop sending data. The sink typically uses backpressure to stop the flow of data when its FIFO

buffers are full or when it has congestion on its output.

Related Information

•

NCO IP Core Signals

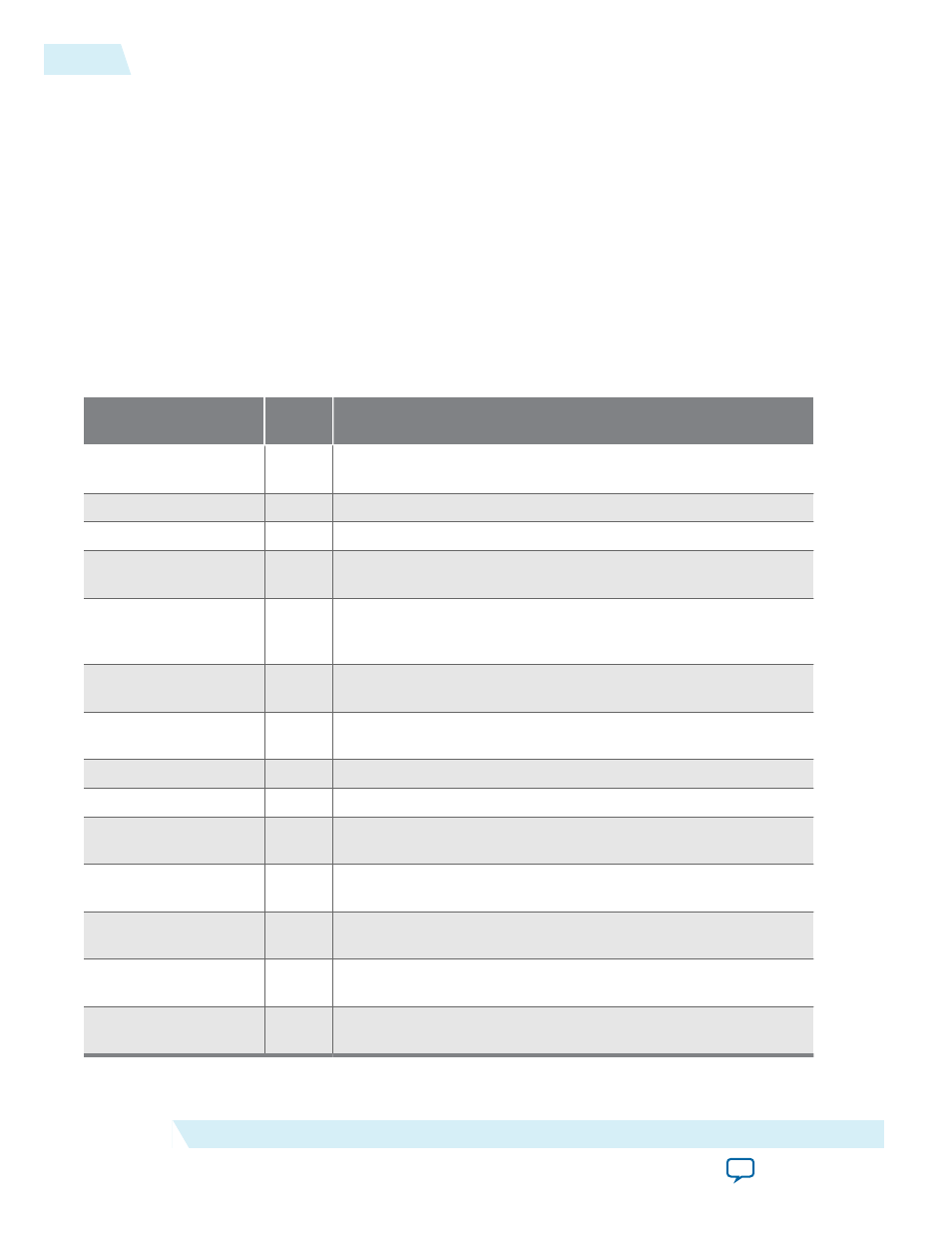

Table 3-6: NCO IP Core Signals

Signal

Directio

n

Description

address[2:0]

Input

Address of the 16 phase increment registers when frequency

hopping is enabled.

clk

Input

Clock.

clken

Input

Active-high clock enable.

freq_mod_i [F-

1:0]

Input

Optional frequency modulation input. You can specify the

modulator resolution F in IP Toolbench.

freq_sel[log

2

N-

1:0]

input

Use to select one of the phase increment registers (that is to

select the hopping frequencies), when frequency hopping is

enabled. N is the depth.

phase_mod_i [P-

1:0]

Input

Optional phase modulation input. You can specify the

modulator precision P in Ithe wizard.

phi_inc_i [A-1:0]

Input

Input phase increment. You can specify the accumulator

precision A in the wizard.

reset_n

Input

Active-low asynchronous reset.

write_sig

Input

Active-high write signal when frequency hopping is enabled.

in_data

Output In Qsys systems, this Avalon-ST-compliant data bus includes all

the Avalon-ST input data signals.

fcos_o [M-1:0]

Output Optional output cosine value (when dual output is selected). You

can specify the magnitude precision M in IP Toolbench.

fsin_o [M-1:0]

Output Output sine value. You can specify the magnitude precision M in

IP Toolbench.

out_valid

Output Data valid signal. Asserted by the MegaCore function when there

is valid data to output.

out_data

Output In Qsys systems, this Avalon-ST-compliant data bus includes all

the Avalon-ST output data signals.

3-10

NCO IP Core Signals

UG-NCO

2014.12.15

Altera Corporation

NCO IP Core Functional Description