Nco design example specification, Nco design example specification -2 – Altera NCO MegaCore Function User Manual

Page 32

The following directories contain separate top-level design files (named

multichannel_example.v

and

multichannel_example.vhd

) for Verilog HDL and VHDL in the directories:

<IP install path>\nco\example_designs\multi_channel\verilog

<IP install path>\nco\example_designs\multi_channel\vhdl

NCO Design Example Specification

The NCO meets the following specifications:

• SFDR: 110 dB

• Output Sample Rate: 200 MSPS (50 MSPS per channel)

• Output Frequency: 5MHz, 2MHz, 1MHz, 500KHz

• Output Phase: 0, π/4, π/2, π

• Frequency Resolution: 0.047 Hz

• Clock rate = 200MHz clock rate

• Number of channels = 4.

• Output sample-rate = f

clk

/4.

• Maximum output clock frequency = 50MHz.

The output signal has only one sample for a cycle.

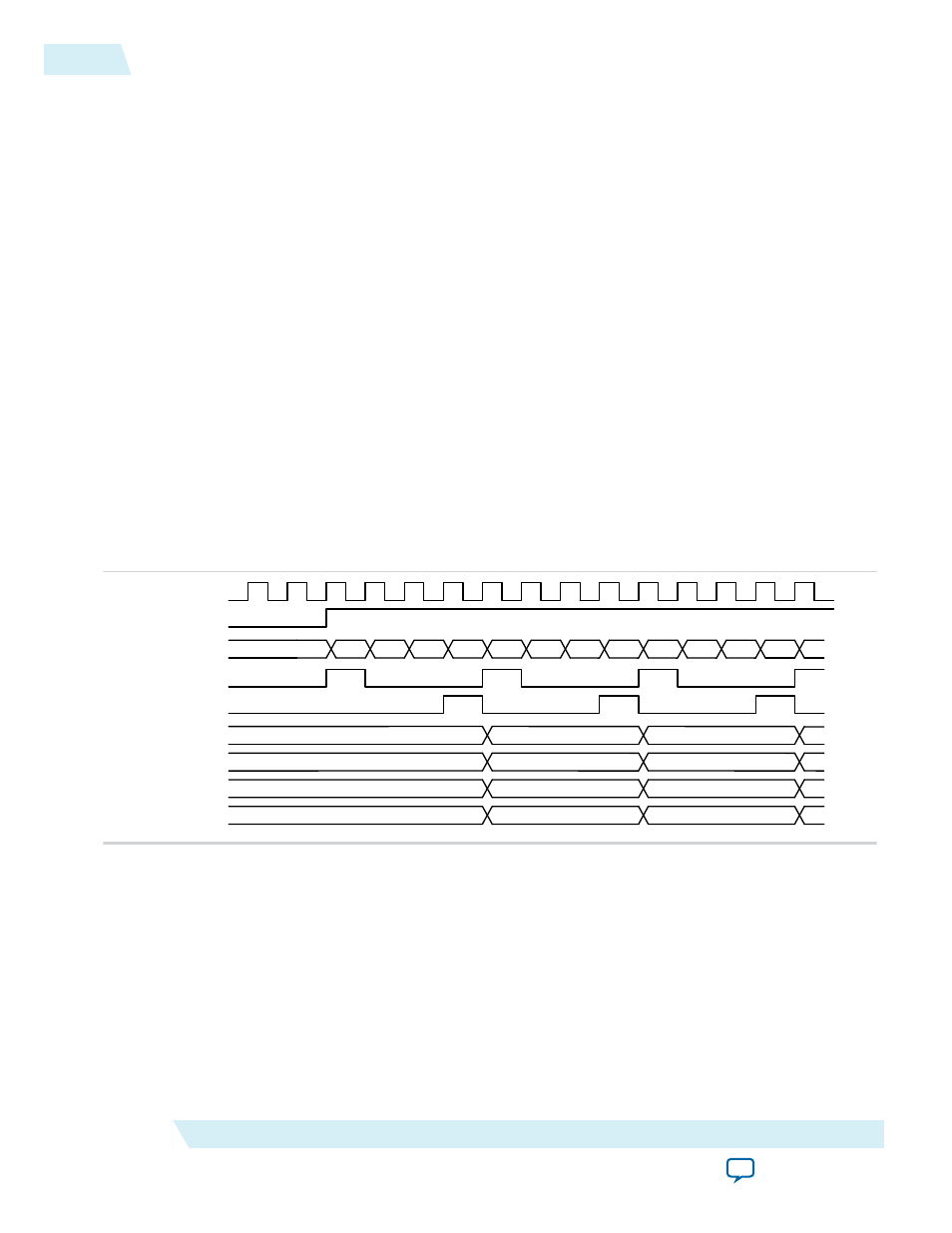

Figure 4-2: Multi-Channel NCO Output SignalsShows the timing relationship between Avalon-ST

signals, a generated multiplexed signal stream and demultiplexed signal streams

clk

valid

startofpacket

endofpacket

sin_o

sin_ch0

sin_ch1

sin_ch2

sin_ch3

A0

B0

C0

D0

A1

B1

C1

D1

A2

B2

C2

D2

A0

B0

C0

D0

A1

B1

C1

D1

Design Example Parameters

4-2

NCO Design Example Specification

UG-NCO

2014.12.15

Altera Corporation

NCO Multichannel Design Example