Altera Partial Reconfiguration IP Core User Manual

Page 14

1. Avalon Memory Mapped Master component writes

16’h0001

(or

16’h0003

if the design requires

double PR) to this IP address offset 0x1 to trigger PR operation.

2. Avalon Memory Mapped Master component writes PR bitstream (data width in x16) to this IP address

offset 0x0 until all the PR bitstream is written.

3. Avalon Memory Mapped Master component reads the data from this IP address offset 0x1 to check

the

status[2:0]

value. Optionally, Avalon-MM Master component can read the

status[2:0]

of this

IP during PR operation to understand if any early failure was detected, for example,

PR_ERROR

.

Related Information

•

Partial Reconfiguration IP Core Parameters

•

Avalon Memory Map Slave Interface Read and Write Transfer Timing

on page 17

For more information on the timing specification for the Avalon Memory Mapped Slave interface.

Avalon Memory Map Slave Interface Data/CSR Memory Map

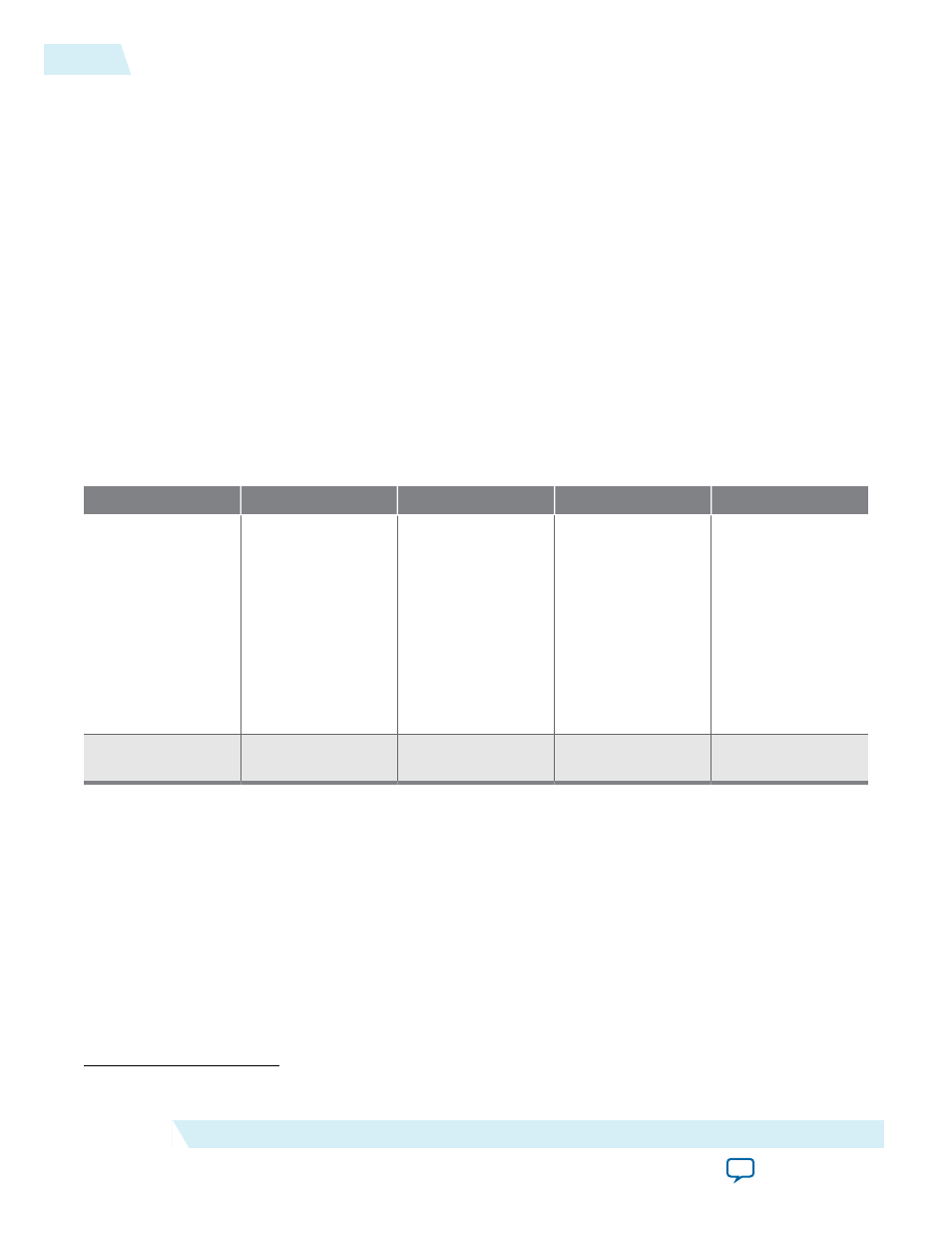

Table 6: Data/CSR Memory Map Format

Name

Address Offset

Width

Access

Description

PR_DATA

0x0

16 or 32

(1)

Write

Every data

write

to this address

indicates this

bitstream was

sent to the IP

core.

Performing a

read

on this

address returns

all 0's.

PR_CSR

0x1

16 or 32

(1)

Read/Write

Controls and

status registers.

(1)

Depending on the Avalon Memory Mapped data bus width.

14

Avalon Memory Map Slave Interface Data/CSR Memory Map

UG-PARTRECON

2015.05.04

Altera Corporation

Partial Reconfiguration IP Core