Altera Partial Reconfiguration IP Core User Manual

Page 9

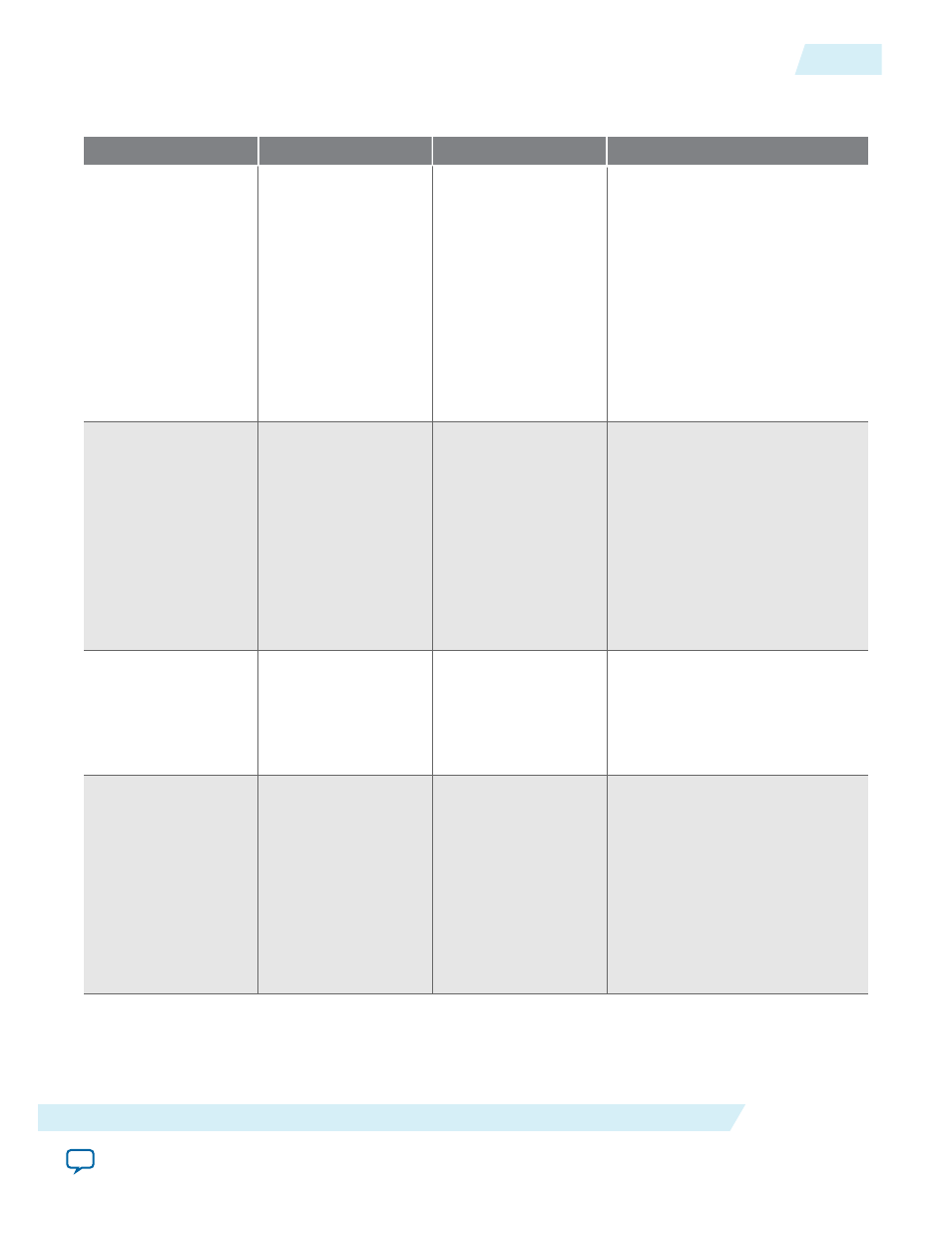

Table 3: Conduit Interface

These options are available when Enable Avalon-MM slave interface parameter is turned Off.

Port Name

Width

Direction

Function

pr_start

1

Input

A signal arriving at this port

asserted high initiates a PR

event. You must assert this signal

high for a minimum of one clock

cycle and de-assert it low prior to

the end of the PR operation so

that the PR IP core is ready to

accept the next

pr_start

trigger

event when the

freeze

signal is

low.

This signal is ignored during

JTAG debug operations.

data[]

1, 2, 4, 8, 16, or 32

Input

Selectable input PR data bus

width, either x1, x2, x4, x8, x16,

or x32.

Once a PR event is triggered, it is

synchronous with the rising edge

of the

clk

signal whenever the

data_valid

signal is high and

the

data_read

signal is high.

This signal is ignored during

JTAG debug operations.

data_valid

1

Input

A signal arriving at this port

asserted high indicates the

data[]

port contains valid data.

This signal is ignored during

JTAG debug operations.

data_ready

1

Output

A signal arriving at this port

asserted high indicates the PR IP

core is ready to read the valid

data on the

data[]

port

whenever the

data_valid

signal

is asserted high. The data sender

must stop sending valid data if

this port is low.

This signal deasserted low

during JTAG debug operations.

UG-PARTRECON

2015.05.04

Partial Reconfiguration IP Core Ports

9

Partial Reconfiguration IP Core

Altera Corporation