Bit error count, Interfaces, Bit error count –6 – Altera Reed-Solomon Compiler User Manual

Page 24: Interfaces –6

3–6

Chapter 3: Functional Description

Interfaces

Reed-Solomon Compiler

December 2014

Altera Corporation

User Guide

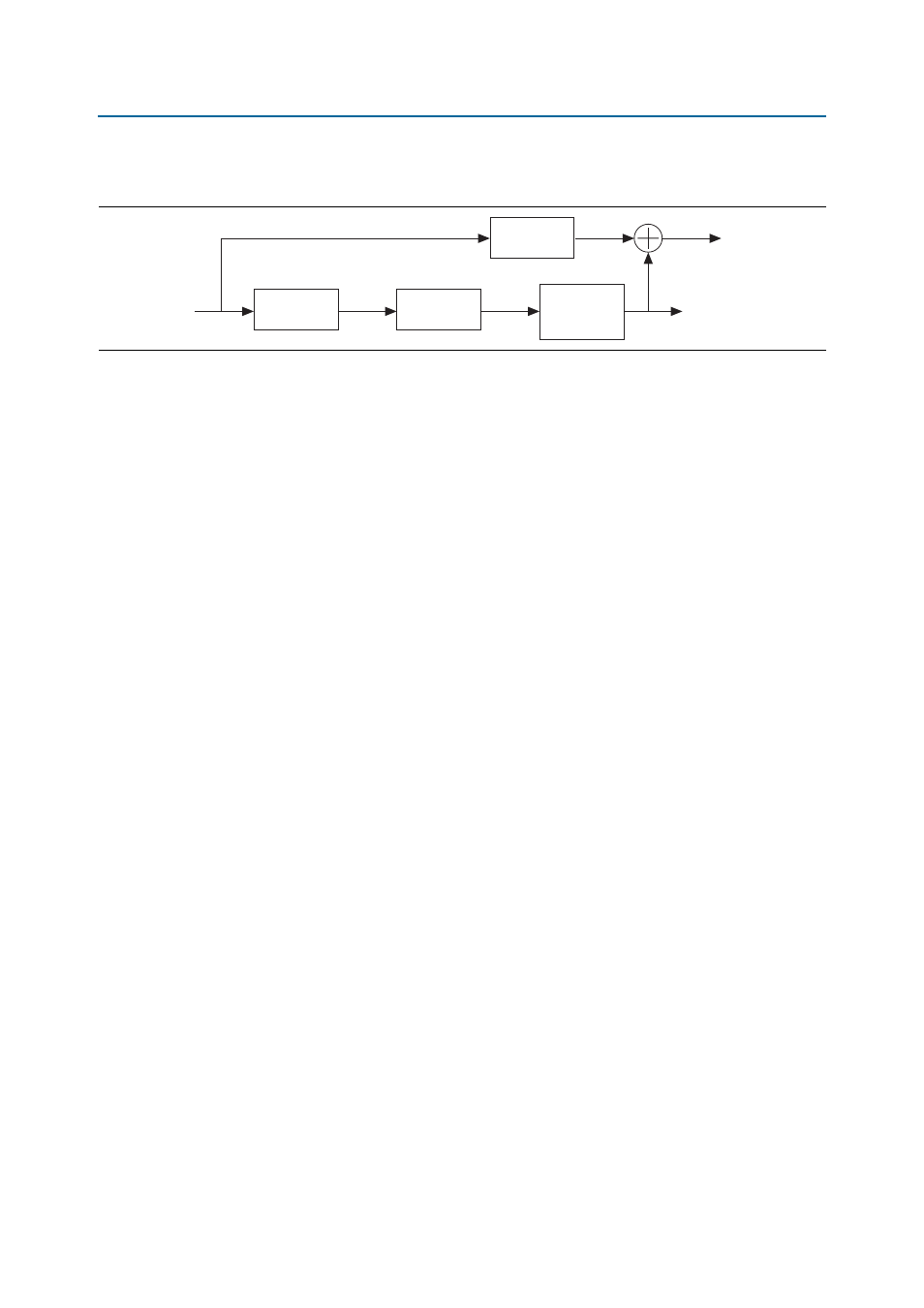

shows the error symbol output.

Whenever rserr is not 0 (while decfail is 0), an error correction successfully takes

place. The rsout is the rserr XORed with the corresponding rsin, where XOR is done

for each bit, so you know that the respective symbol has been corrected. The value of

rserr

shows which bits of the symbol have been corrected. For each bit of rserr that

is 1, the corresponding bit of rsout is corrected.

The rsout and the corresponding rserr value appear at the output at the same clock

cycle.

Bit Error Count

The decoder can provide the bit error count found in the correction process. The bit

error count has the following options:

■

Full count. The output num_err_bit is connected, which shows the valid value.

■

Split count. The outputs num_err_bit0 and num_err_bit1 are connected, which

show the valid values

For information about these outputs, refer to

.

Interfaces

The RS encoder and decoder use the Avalon

®

Streaming (Avalon-ST) interface for data

input and output. The input is an Avalon-ST sink and the output is an Avalon-ST

source. The Avalon-ST interface READY_LATENCY parameter is set to 1. The Avalon-ST

interfaces allow for flow control.

The Avalon-ST interface is an evolution of the Atlantic

™

interface. The Avalon-ST

interface defines a standard, flexible, and modular protocol for data transfers from a

source interface to a sink interface and simplifies the process of controlling the flow of

data in a datapath. The Avalon-ST interface signals can describe traditional streaming

interfaces supporting a single stream of data without knowledge of channels or

packet boundaries. Such interfaces typically contain data, ready, and valid signals.

The Avalon-ST interface can also support more complex protocols for burst and

packet transfers with packets interleaved across multiple channels. The Avalon-ST

interface inherently synchronizes multi-channel designs, which allows you to achieve

efficient, time-multiplexed implementations without having to implement complex

control logic.

Figure 3–5. Error Symbol Output

Memory

& Control

Syndrome

Calculation

rsin

rserr

rsout

Solve Key

Equation

Chien Search

& Forney's

Algorithm