Altera Reed-Solomon Compiler User Manual

Page 27

Chapter 3: Functional Description

3–9

Signals

December 2014

Altera Corporation

Reed-Solomon Compiler

User Guide

shows the Avalon-ST sink (data input) interface.

shows the Avalon-ST source (data output) interface.

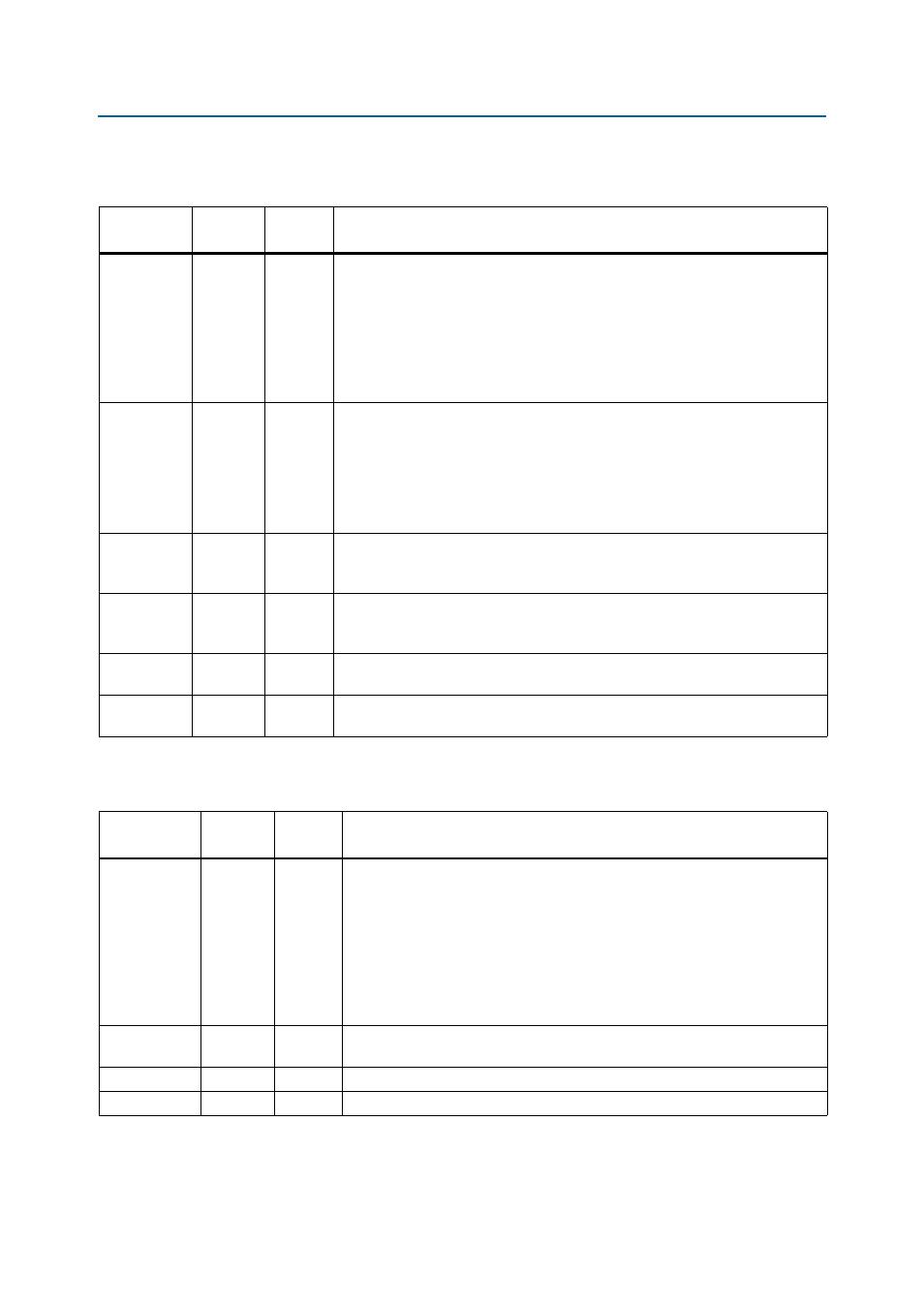

Table 3–5. Avalon-ST Sink Interface

Name

Avalon-ST

Type

Direction

Description

sink_ena

ena

Output

Data transfer enable signal. sink_ena is driven by the sink interface and controls

the flow of data across the interface. sink_ena behaves as a read enable from sink

to source. When the source observes sink_ena asserted on the clk rising edge it

drives, on the following clk rising edge, the Avalon-ST data interface signals and

asserts val, if data is available. The sink interface captures the data interface

signals on the following clk rising edge. If the source is unable to provide new

data, it de-asserts val for one or more clock cycles until it is prepared to drive valid

data interface signals.

sink_val

val

Input

Data valid signal. sink_val indicates the validity of the data signals. sink_val is

updated on every clock edge where sink_ena is asserted. sink_val and the dat

bus hold their current value if sink_ena is de-asserted. When sink_val is

asserted, the Avalon-ST data interface signals are valid. When sink_val is de-

asserted, the Avalon-ST data interface signals are invalid and must be disregarded.

To determine whether new data has been received, the sink interface qualifies the

sink_val

signal with the previous state of the sink_ena signal.

sink_sop

sop

Input

Start of packet (codeword) signal. sop delineates the codeword boundaries on the

rsin

bus. When sink_sop is high, the start of the packet is present on the rsin

bus. sink_sop is asserted on the first transfer of every codeword.

sink_eop

eop

Input

End of packet (codeword) signal. sink_eop delineates the packet boundaries on the

rsin

bus. When sink_eop is high, the end of the packet is present on the dat bus.

sink_eop is asserted on the last transfer of every packet.

rsin[m:1]

data

Input

Data input for each codeword, symbol by symbol. Valid only when sink_val is

asserted.

eras_sym

data

Input

When asserted, the symbol in rsin[] is marked as an erasure. Valid only for the

decoder with Erasures-supporting decoder option.

Table 3–6. Avalon-ST Source Interface (Part 1 of 2)

Name

Avalon-ST

Type

Direction

Description

source_ena

ena

Input

Data transfer enable signal. source_ena is driven by the sink interface and

controls the flow of data across the interface. ena behaves as a read enable from

sink to source. When the source interface observes source_ena asserted on the

clk

rising edge it drives, on the following clk rising edge, the Avalon-ST data

interface signals and asserts source_val when data from sink interface is

available. The sink interface captures the data interface signals on the following

clk

rising edge. If this source is unable to provide new data, it de-asserts

source_val

for one or more clock cycles until it is prepared to drive valid data

interface signals.

source_val

val

Output

Data valid signal. source_val is asserted high, whenever there is a valid output on

rsout

; it is de-asserted when there is no valid output on rsout.

source_sop

sop

Output

Start of packet (codeword) signal.

source_eop

eop

Output

End of packet (codeword) signal.