Stratix ii gx embedded gigabit ethernet mac / phy – Altera Stratix II GX Embedded Gigabit Ethernet MAC/PHY User Manual

Page 11

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

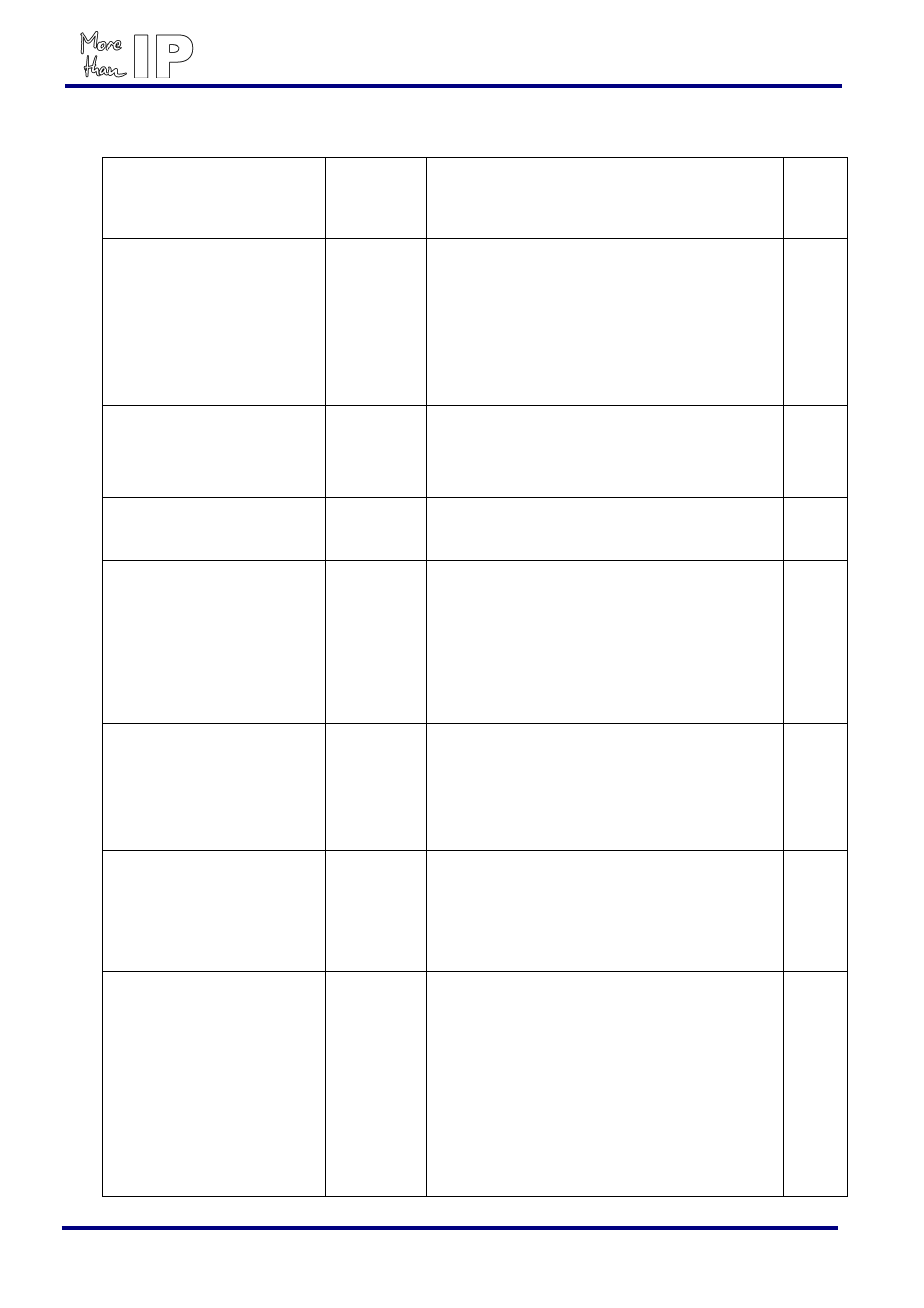

Frame length increment

Bytes

Frame payload length increment. During

simulation frames are generated starting from

"length of first frame" incrementing with each

frame generated.

1

Generated Frames max.

payload length

Bytes

Defines the payload maximum length used by the

Ethernet Generator models. This value specifies

the wrap around for the frame length of generated

frames. I.e. if the frame length increment would

exceed this value it wraps around to zero. Can be

used to test frame length error detection, when set

to any value larger than the MAC length

configuration.

1500

Enable Padding of Frames in

RX Path

Boolean

If enabled, RX PHY Generator model generated

frames are padded to 64 octets in length (normal

mode). If disabled, no padding occurs and

erroneous frames will be sent to the MAC RX.

True

Enable VLAN frames for all

tests

Boolean

If enabled, all frames sent/received will be VLAN

type of frames

False

Stop RX FIFO read after

Frames

Inhibits the Testbench RX FIFO monitor reading

the RX FIFO, after this amount of frames has

been sent to the RX.

Can be used to test Flow-Control behaviour. If

more frames are received, the FIFO will get filled.

When the threshold level is reached, a Pause-

Frame will be generated by the MAC TX. If set to

0, the RX FIFO read is never paused.

0

Restart RX FIFO read after

RX FIFO

clocks

Number of clock cycles, the RX FIFO should not

be read after it has been stopped. Only relevant if

the previous configuration (read stop) was set to a

non-null value.

After this number of RX FIFO clock cycles, the RX

FIFO will be emptied again.

10

Generate Frames with Errors

on Transmit FIFO Interface

Boolean

Enable Transmit Error Generation the Core

Transmit Interface. When selected, the transmit

FIFO signal ff_tx_err is asserted with

ff_tx_eop

to signal an Error. When disabled,

the FIFO error is signalled, ff_tx_err is never

set to '1'.

False

Testbench reacts on Pause

Frames

Boolean

If enabled (true) the Testbench will stop the RX

(PHY) Frame generator, if the MAC sends a

Pause Frame. This simulates a usual flow-control

chain correctly.

If disabled (False) Pause Frames sent by the

MAC are ignored by the Testbench and the RX

(PHY) Frame generator will never pause. This can

be used to test the MACs FIFO overflow behavior.

This option has no effect, if loopback mode is

enabled (i.e. Frame generation in RX path is set

0).

True

11