3 design kit database, 4 simulation environment, Esign – Altera Stratix II GX Embedded Gigabit Ethernet MAC/PHY User Manual

Page 7: Atabase, Imulation, Nvironment, Table 1: core configuration options, Table 2: design kit directory structure, Stratix ii gx embedded gigabit ethernet mac / phy

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

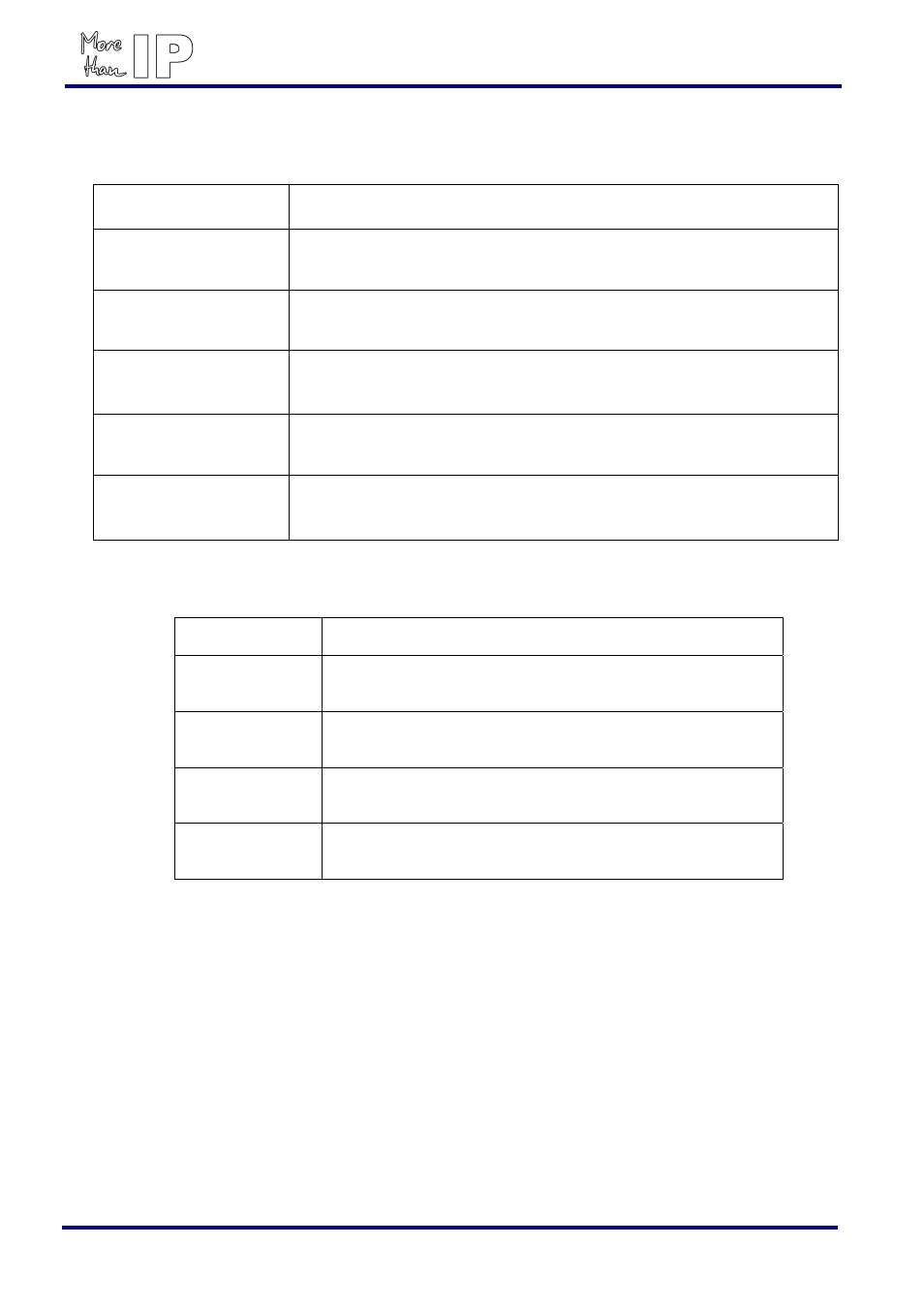

Table 1: Core Configuration Options

Option Description

Technology

The Core is optimized for Altera Stratix II GX devices.

Maximum Frame Length

Maximum Frame Length. Defines a 14-Bit maximum frame length used by

the MAC receive logic to check frames.

Pause Frame Quanta

Receive Pause Quanta. 16-Bit value sets, in increment of 512 Ethernet bit

times, the pause quanta used in each Pause Frame sent to the remote

Ethernet device.

Enable Promiscuous

Receive Mode

When selected, all frames are received without Unicast address filtering.

Insert MAC Address on

Transmit

If select the MAC overwrites the source MAC address with the MAC set on

the Core signal mac_addr. If disabled, the source MAC address received

from the transmit application transmitted is not modified by the MAC.

3.3 Design Kit Database

Table 2: Design Kit Directory Structure

Directory Description

models

Ethernet Frame generator and monitor models.

quartus

Contains the netist for Altera Stratix implementation and a script

to control the Altera Quartus design software.

simulation

Scripts to configure and execute RTL and Gate-Level Simulation

as well the Modelsim integrated TestBuilder.

source

Encrypted VHDL design source files, testbench and

configuration files.

3.4 Simulation Environment

A complete testbench is provided (File testbench.vhd in directory source/testbench/vhdl)

which implements the Core together with a simulation control state machine and the following

drivers and monitors.

• GMII Ethernet Frame Generator: Configurable Ethernet Gigabit Ethernet frame generator

with GMII interface.

• GMII Ethernet Frame Monitor: Gigabit Ethernet frame monitor with GMII interface.

• Ethernet Frame Generator (FIFO mode): Configurable Ethernet frame generator

simulating a user application connected to the MAC transmit FIFO interface.

• Ethernet Monitor (FIFO mode): Ethernet frame checker simulating a user application

connected to the MAC receive FIFO interface.

• PCS: 1000Base-X PCS function that decodes / encodes data from / to the MAC / PHY

Core and controls the Auto-Negotiation process within the testbench.

7