Overview, Simulation options, Unning – Altera Stratix II GX Embedded Gigabit Ethernet MAC/PHY User Manual

Page 13: Imulation, Sing, Odelsim, Table 5: testbuilder simulation control, Table 6: simulation options, Stratix ii gx embedded gigabit ethernet mac / phy

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

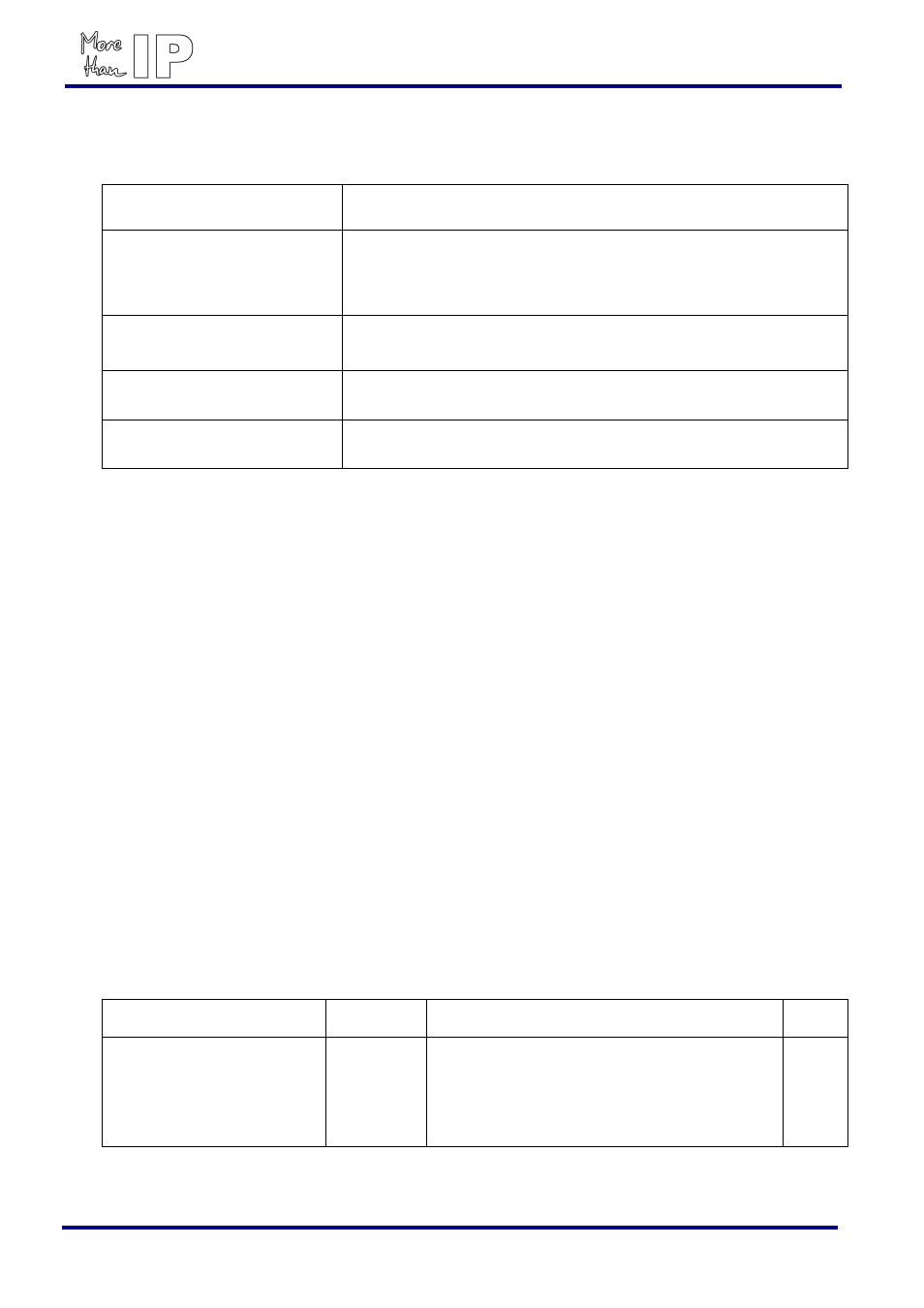

Table 5: Testbuilder Simulation Control

Testbuilder Panel Option

Description

Compile Database before

Simulation (VHDL)

When enabled, the Core simulation database is refreshed with the Core

configuration options. The option must be enabled at least once after a

new Core database was generated.

Run Simulation Only

When selected, starts the RTL simulation with all the options defined in

the Testbuilder panel ignored (Previous configuration used).

Configure and Start Simulation

When selected, the options defined on the Testbuilder panel are saved

before the RTL simulation is performed.

Run Gate-Level

When selected, the options defined on the Testbuilder panel are saved

before the Gate level simulation is performed.

When running a simulation, a set of waveforms is displayed; error and information messages are

issued in the Modelsim standard output.

3.6 Running Simulation Using Modelsim PE or Modelsim AE

Overview

Modifying the file mtip_sim_pack.vhd located in the directory source/package/vhdl

creates a custom simulation scenario. The Core files and dependencies are available in the file

comp.do

(In Directory simulation), the testbench file and simulation models files are listed

in the file sim.do. The files comp.do and sim.do should be modified and adapted with the

simulator command.

Once a scenario has been created, the following steps should be followed:

1. Change to the simulation directory.

2. Compile the Core database:

• do comp.do

3. Compile the Simulation database and run simulation:

• do sim.do

Simulation Options

The simulation is controlled and is configured with a set of parameters set in the file

mtip_sim_pack.vhd

.

Table 6: Simulation Options

Option Unit

Description

Default

TB_RXFRAMES Frames

Sets the number of frames that are generated by

the Ethernet frame Generator connected to the

Receive PHY interface.

If set to 0, a Serdes loopback test is performed

with the Core pin loop_ena set to '1'.

5

13