Measuring power, A/d measurements, Measuring power –3 – Altera Stratix III User Manual

Page 21: A/d measurements –3, Measuring core power –3 measuring i/o power –3

Chapter 5: Power Measurement

5–3

Measuring Power

© August 2008

Altera Corporation

Stratix III Development Kit User Guide

Measuring Power

You can measure power by using the analog-to-digital (A/D) circuitry on the

development board or by using a digital multimeter (DMM) across on-board sense

resistors. However, note that, depending on the DMM accuracy, the on-board A/D

measurements tend to produce considerably more accurate results.

A/D Measurements

The POWER SELECT rotary switch SW6 sets the development board to measure and

display FPGA core power or I/O output power (

Measuring Core Power

To measure FPGA core power for various power states, perform the following steps:

1. Ensure that the 8-position SW2 DIP switch is configured to the default settings

shown in

.

2. Download the stratixIII_dev_power.sof file as described in

. The power design example is in

<path>\demos\stratixIII_3sl150_dev_power.

3. Set the POWER SELECT rotary switch SW6 to 0 to measure the internal V

CC_INT

power in watts.

4. Observe the power on the 4-digit hexadecimal POWER DISPLAY.

5. Using the user input push buttons (

), advance through the

power states in

. Notice how power increases

as frequency and resources increase.

Measuring I/O Power

This example uses FPGA I/O banks 2, 4, 5, and 6. Using the SW6 settings (

),

measure the power for I/O banks 4, 5, and 6, then for I/O bank 2, by performing the

following steps:

1. Ensure that the 8-position SW2 DIP switch is configured to the default settings

shown in

.

2. Download the stratixIII_dev_power.sof file as described in

. The power design example is in

<path>\demos\stratixIII_3sl150_dev_power.

3. Set the POWER SELECT rotary switch SW6 to 8.

4. Observe the 4-digit hexadecimal POWER DISPLAY for the I/O output power in

watts on banks 4, 5, and 6.

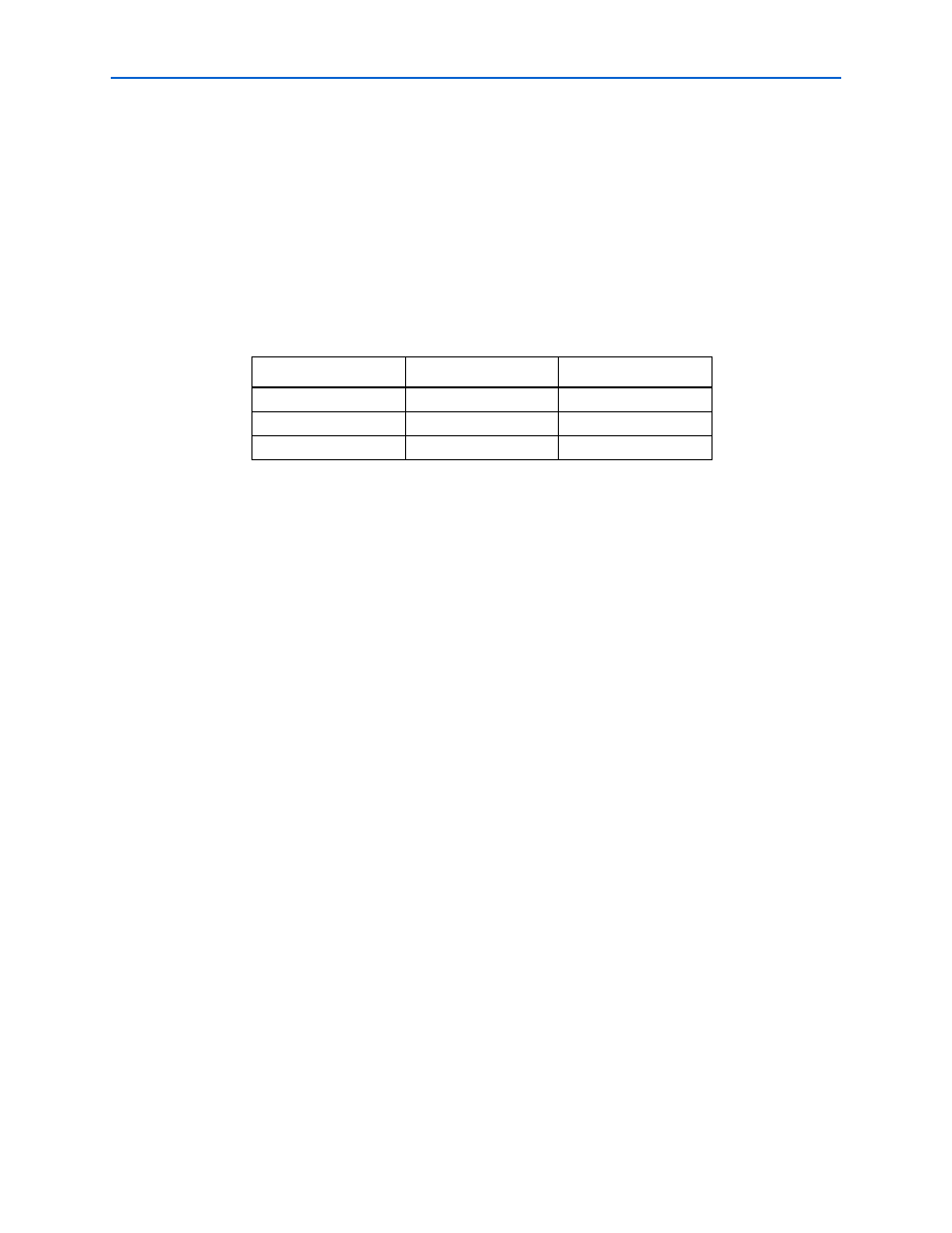

Table 5–4. Switch SW6 Power Selection

Switch Position

FPGA Power

I/O Bank

0

Core: VCCL, TBD V

—

7

I/O: 2.5 V

2

8

I/O: 2.5 V

4, 5, and 6