Ddr sdram – Altera Cyclone III FPGA Starter Board User Manual

Page 23

Altera Corporation

2–15

April 2012

Cyclone III FPGA Starter Board Reference Manual

Board Components and Interfaces

DDR SDRAM

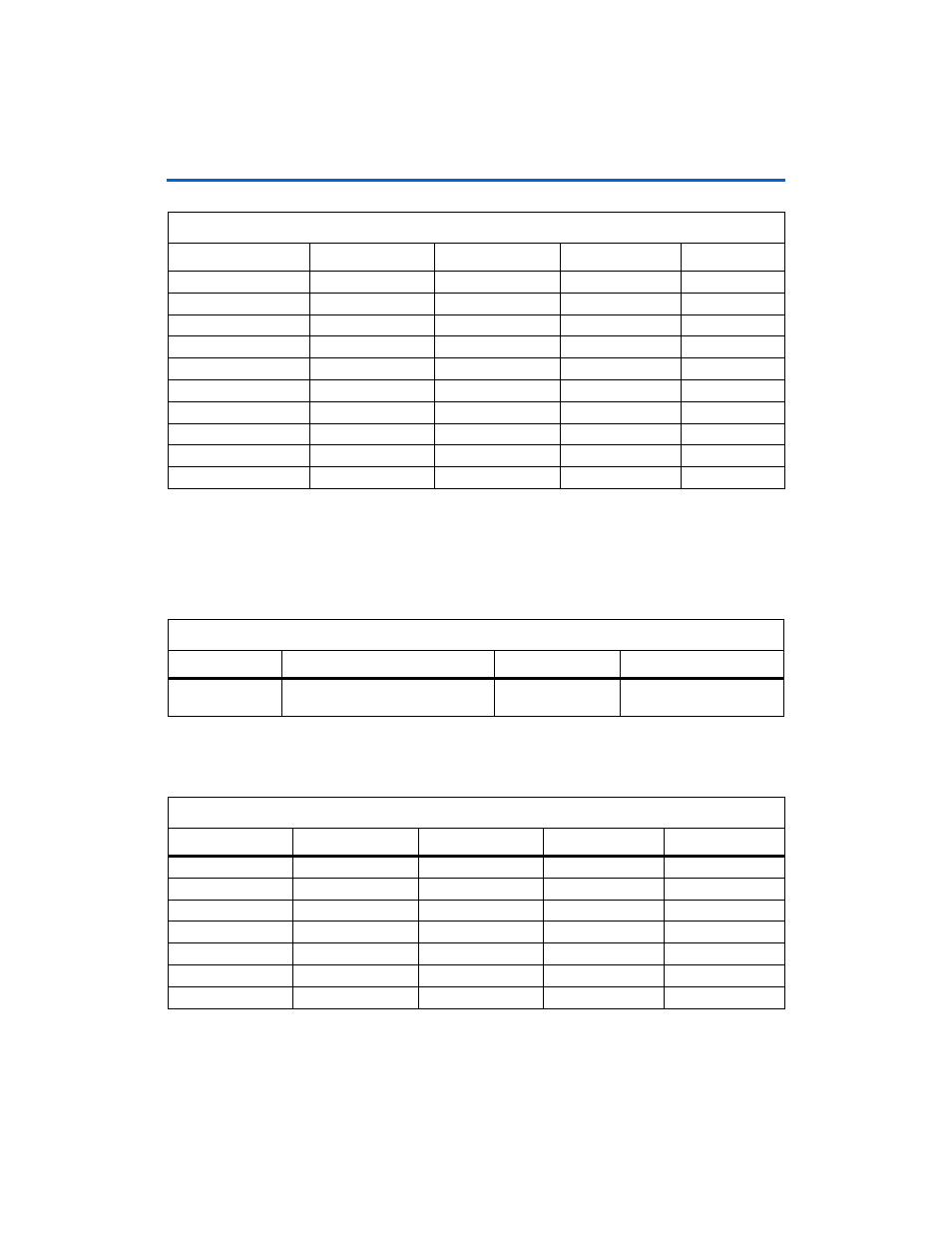

The Cyclone III FPGA starter board has a 4M x 16 x 4 DDR SDRAM.

Table 2–13

lists DDR SDRAM board reference and manufacturing

information.

Table 2–14

shows the DDR SDRAM signal name, corresponding FPGA

pin, signal direction, type, and board reference U4 DDR pin.

flash_sram_dq13

B5 Bidirectional

2.5

V

H5

flash_sram_dq14

A5 Bidirectional

2.5

V

G7

flash_sram_dq15

B6 Bidirectional

2.5

V

E7

flash_we_n

D18

Output

2.5 V

G8

flash_ce_n

E2 Output

2.5 V

B4

flash_oe_n

D17 Output

2.5 V

F8

flash_reset_n

C3 Output

2.5 V

D4

flash_adv_n

H14 Output

2.5 V

F6

flash_clk (dclk)

H4

Output

2.5 V

E6

flash_wait

H13 Output

2.5 V

F7

Table 2–12. Parallel Flash Memory Pinout (Part 3 of 3)

Signal Name

FPGA Pin

Direction

Type

U6 (Flash) Pin

Table 2–13. DDR SDRAM Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturer Part Number

U4

4M x16 x 4 DDR SDRAM

PowerChip

Semiconductor

A2S56D40CTP-G5PP

Table 2–14. DDR SDRAM Pinout (Part 1 of 3)

Signal Name

FPGA Pin

Direction

Type

U4 (DDR) Pin

ddr_dqs0

U3

Bidirectional

SSTL-2

16

ddr_dqs1

T8 Bidirectional

SSTL-2

51

ddr_dm0

V3 Output

SSTL-2

47

ddr_dm1

V8

Output

SSTL-2

20

ddr_ba0

V11 Output

SSTL-2

26

ddr_ba1

V12 Output

SSTL-2

27

ddr_cas_n

T4 Output

SSTL-2

22