Analog Way DI-VENTIX II - Ref. DVX8044 Programmer's Guide User Manual

Page 6

6

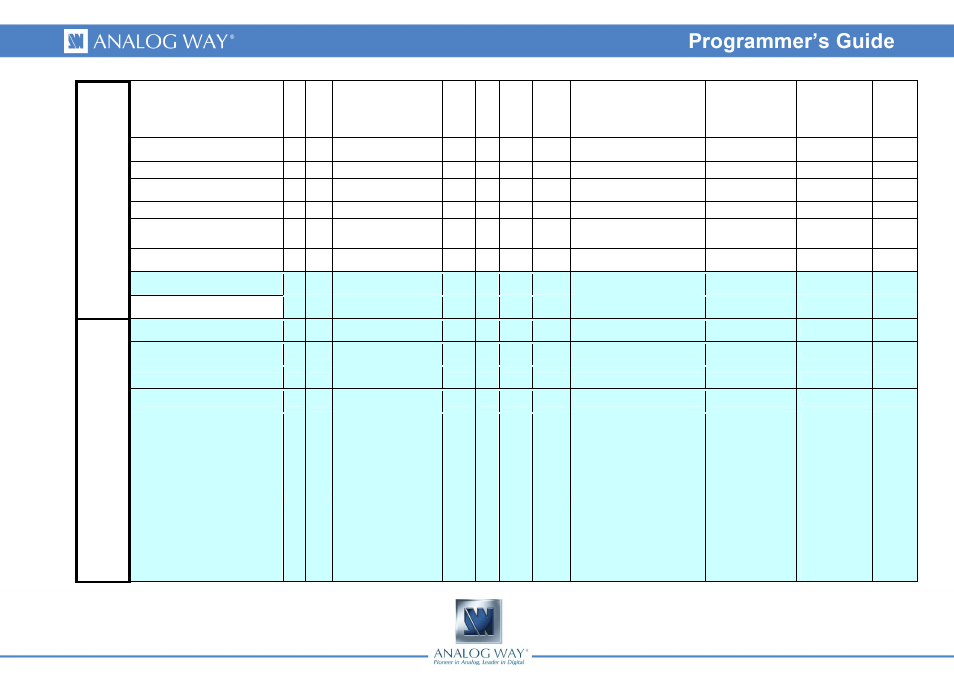

SWITCHER_MODE

CM CM

Device mode

Rd/Wr 0

3

0

0 = Mixer mode

1 = Matrix mode

2 = Embedded softedge mode

3 = Synchronous Matrix mode

AUTO_LOCK

YL

YL

auto-lock (prevent from

no-signal selection)

Rd/Wr 0

1

1

1 = disable selection of inputs

without signal

AUTO_TAKE

YT

YT

auto-take

Rd/Wr 0

1

0

1 = automatic TAKE enable

AUTO_STEPBACK

YA YA

preset toggle

Rd/Wr 0

1

0

1 = exchange Current and Next

presets on TAKE operation

AUTO_SET

YX YX

inputs auto-setting

Rd/Wr 0

1

0

(auto clear)

BUTTON_1_1_MODE

YM YM

front panel key 1:1 mode Rd/Wr 0

1

1

0 = 1_1 key in no zoom mode

1 = 1_1 key in centered mode

NATIVE_ZOOM_REQUEST

YY YY

current layer 1:1 scaling

request

Rd/Wr 0

1

0

(auto clear)

HDCP_CONFLICT

HC HC

HDCP conflict

Rd

0

1

0

1 = input HDCP content and at

least one output not HDCP

BOOT_ERROR_STATUS

BE BE

boot error notification (bit

field)

Rd

0

65535 0

bit field, one bit per card

Version

VERI1

xi

xi

machine ID byte 0 & byte

1

Rd

0

65535 0

ex : AAAA

VERI2

xj

xj

machine ID byte 2 & byte

3

Rd

0

65535 0

ex : AAAA

VERI3

xk

xk

machine ID byte 4 & byte

5

Rd

0

65535 0

ex : AAAA

VERI4

xl

xl

machine ID byte 6 & byte

7

Rd

0

65535 0

ex : AAAA

VERK

xK

xK

programmable

components checksum &

version

Rd

0

65535 0

0 = Micro

1 = In1

2 = In2

3 = Out

4 = Scaler

5 = Video

0 = components

number

1 =

microcontroler

2 = 1st

FPGA/CPLD

3 = 2nd

FPGA/CPLD

4 = 3rd

FPGA/CPLD

5 = 4th

FPGA/CPLD

6 = 5th

FPGA/CPLD

7 = 6th

FPGA/CPLD