14 clock distribution, Figure 4-9, Cpci-6200 clock distribution diagram – Artesyn CPCI-6200 Installation and Use (May 2015) User Manual

Page 98: Functional description

Functional Description

CPCI-6200 Installation and Use (6806800J66E)

98

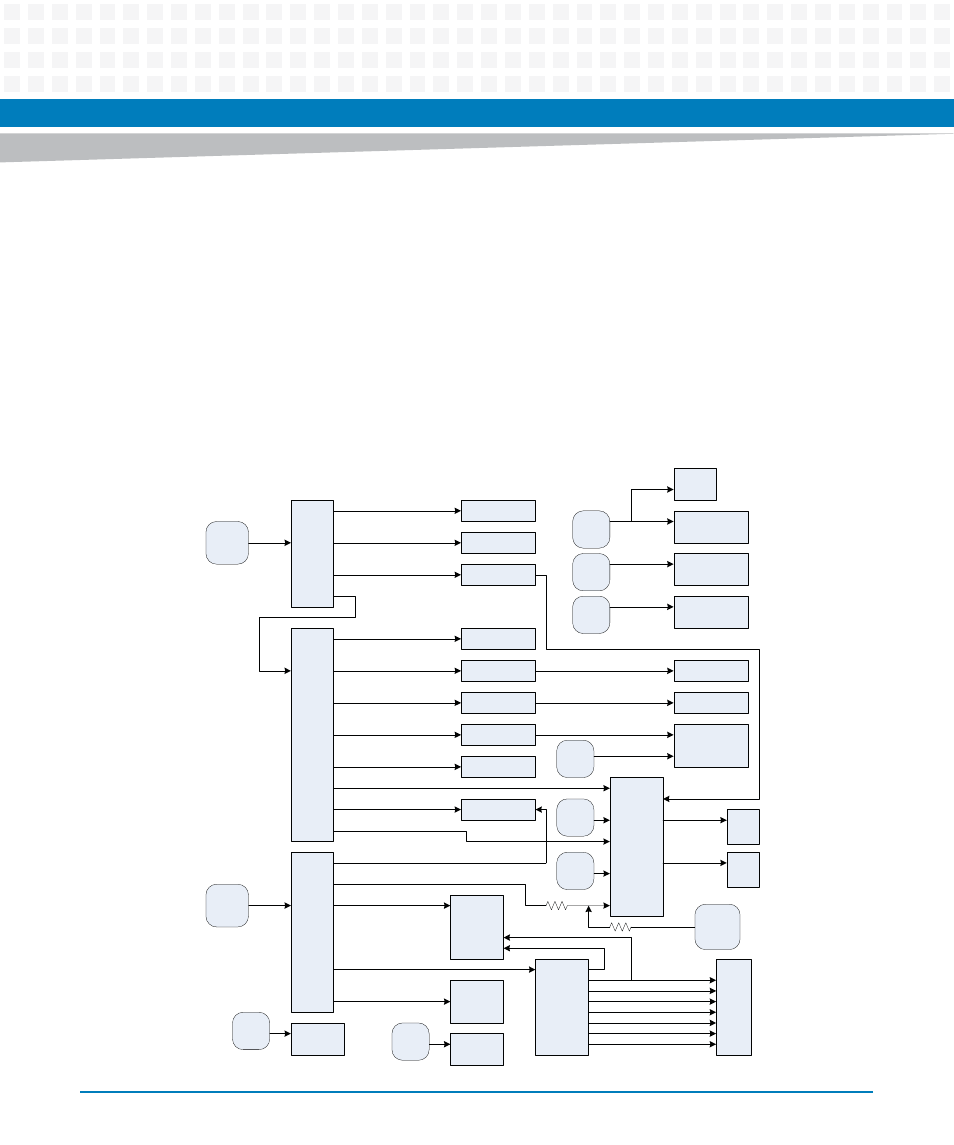

4.14 Clock Distribution

The clock function generates and distributes all of the clocks that are required for system

operation.

The PCI Express clocks are generated using an eight-output differential clock driver. The

PCI/PCI-X bus clocks are generated by the bridge chips from the PCI Express clock. Additional

clocks required by individual devices are generated near the devices using individual

oscillators.

Figure 4-9

CPCI-6200 Clock Distribution Diagram

Clock

Buffer

25MHz

Osc

Diff

Clock

Gen.

(ICS9F

G108)

PHY 1

PHY 1

LBPC CPLD

PCIe Switch

PCI1, TSi384

PMC 1

25MHz

25MHz

25MHz

25MHz

PCIE0_CLK, 100MHz

PCIE1_CLK, 100MHz

CLK_PCI1, 133/100/66MHz

PCI2, TSi384

PMC 2

PCIE2_CLK, 100MHz

CLK_PCI2, 100/66/33MHz

PCI4, TSi381

USB

PCIE4_CLK, 100MHz

CLK_PCI4, 33MHz

48MHz

Osc

Processor

8572

PCIe Expan.

PCIE7_CLK, 100MHz

PCIE5_CLK, 100MHz

PCI3, TSi384

PCIE3_CLK, 100MHz

PCIE6_CLK, 100MHz,

Not Used

66.6 /

100MHz

Osc

125MHz

Osc

SYSCLK

Ethernet

DDR3_CLK1

DDR3_CLK2

PCIe

MPC

9446

PCI

6466

Clock

Buffer

CY2309

QA0

QA1

QB0

CPCI

CPLD

QC0

PCI_BP_CLK0, 33/66MHz

66.6

MHz

Osc

10MHz

Osc

SMUX CPLD

1. 8MHz

Osc

Reset CPLD

8MHz

Osc

H8S IPMI

C_PLD_CLK, 66MHz

PCI_BP_CLK1, 33/66MHz

PCI_BP_CLK2, 33/66MHz

PCI_BP_CLK3, 33/66MHz

PCI_BP_CLK4, 33/66MHz

PCI_BP_CLK5, 33/66MHz

PCI_BP_CLK6, 33/66MHz

P_PB_CLK, 66MHz

CLK_PCI3, 66MHz

S_PB_CLK

33/66MHz

10MHz

Osc

COM 3/4

TL16C552

QC2

CLK_DDR, 66MHz

DDR CLK

32. 6KHz

Crystal

RTC

M41T83

1 MHz

J1 /

J2

DDR3

SO-

DIMM

DDR3

SO-

DIMM

RTC

J5-D19

MXCLK

66.6 MHz

Osc

(Not Used)