Shb a data, Data, Port x – Sundance SMT364 User Manual

Page 13

Version 1.0

Page 13 of 37

SMT364 User Manual

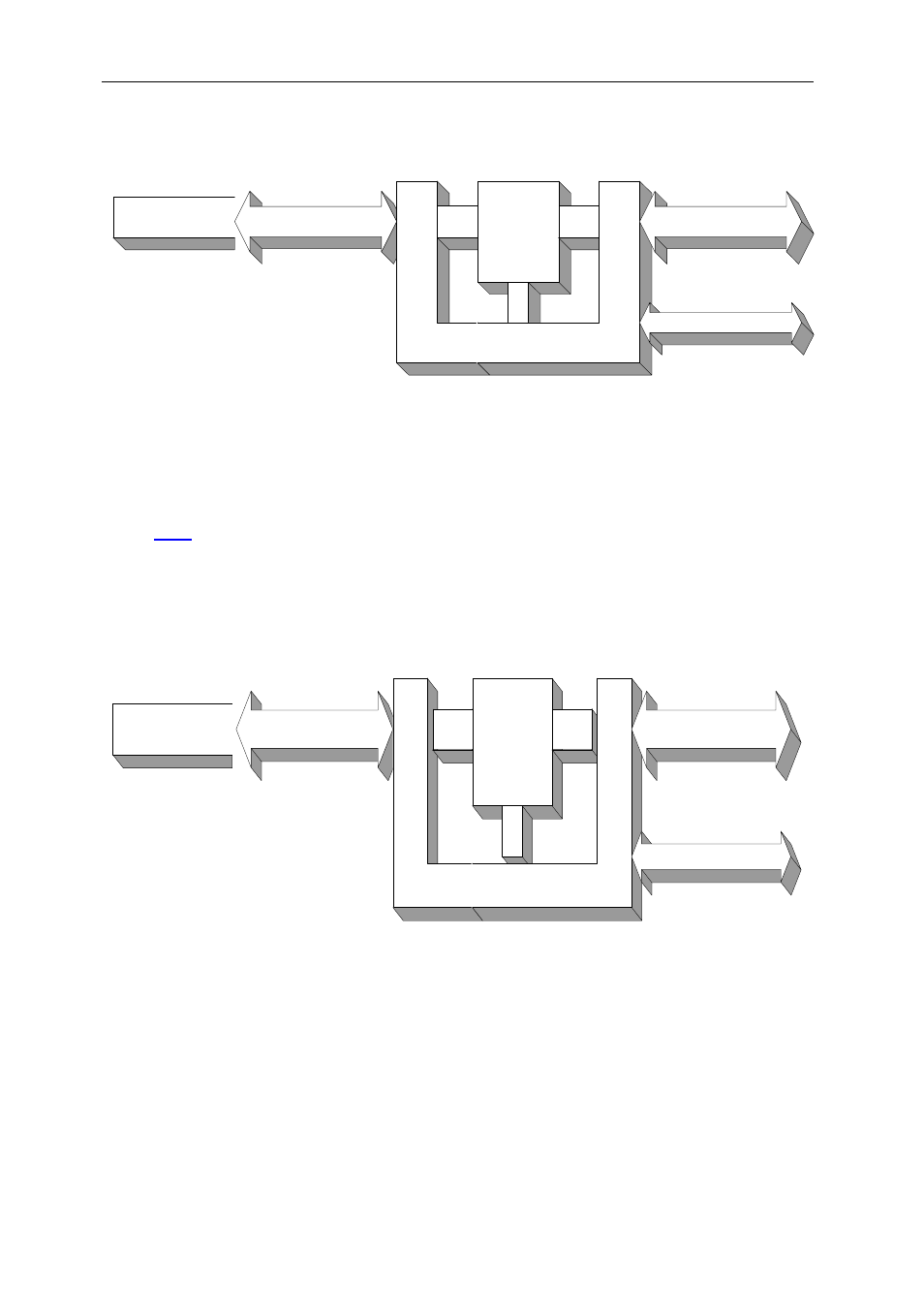

Therefore, as an example, each CommPort can be associated with two 15x32-bit

unidirectional FIFOs implemented into the FPGA; one for input and one for output.

An additional one-word buffer makes them appear as 16x32-bit FIFOs.

DATA

D[0..31]

FIFO

16 x 32 x 2

D[0..7]

Control Logic and Status

STRB RDY REQ ACK

Port x

Figure 3 - CommPort interface data path.

Sundance High-speed Bus - SHB.

Both

SHB

buses are identical and 60-bit wide.

SHBs are parallel communication links for synchronous transmissions. Each SHB

can be divided into two independent 8-bit buses. Each 8-bit bus includes a clock and

three control signals: write enable, request and acknowledge. An SHB bus can also

be divided into two 16-bit buses and one 8-bit bus.

Here is the architecture of the SHB interface implemented into the FPGA:

D[0..31]

FIFO

256 x 32 x 2

D[0..15]

Control Logic and Status

CLK WEN REQ ACK

SHB A

DATA

Figure 4 - SHB interface structure.

Communication links implemented on the SMT364.

The SMT364 provides 4 ComPort links. They are given the numbers 0, 1, 3 and 4.

The default firmware provided with the board implements ComPort4 as a control