Adc performance – Sundance SMT364 User Manual

Page 15

Version 1.0

Page 15 of 37

SMT364 User Manual

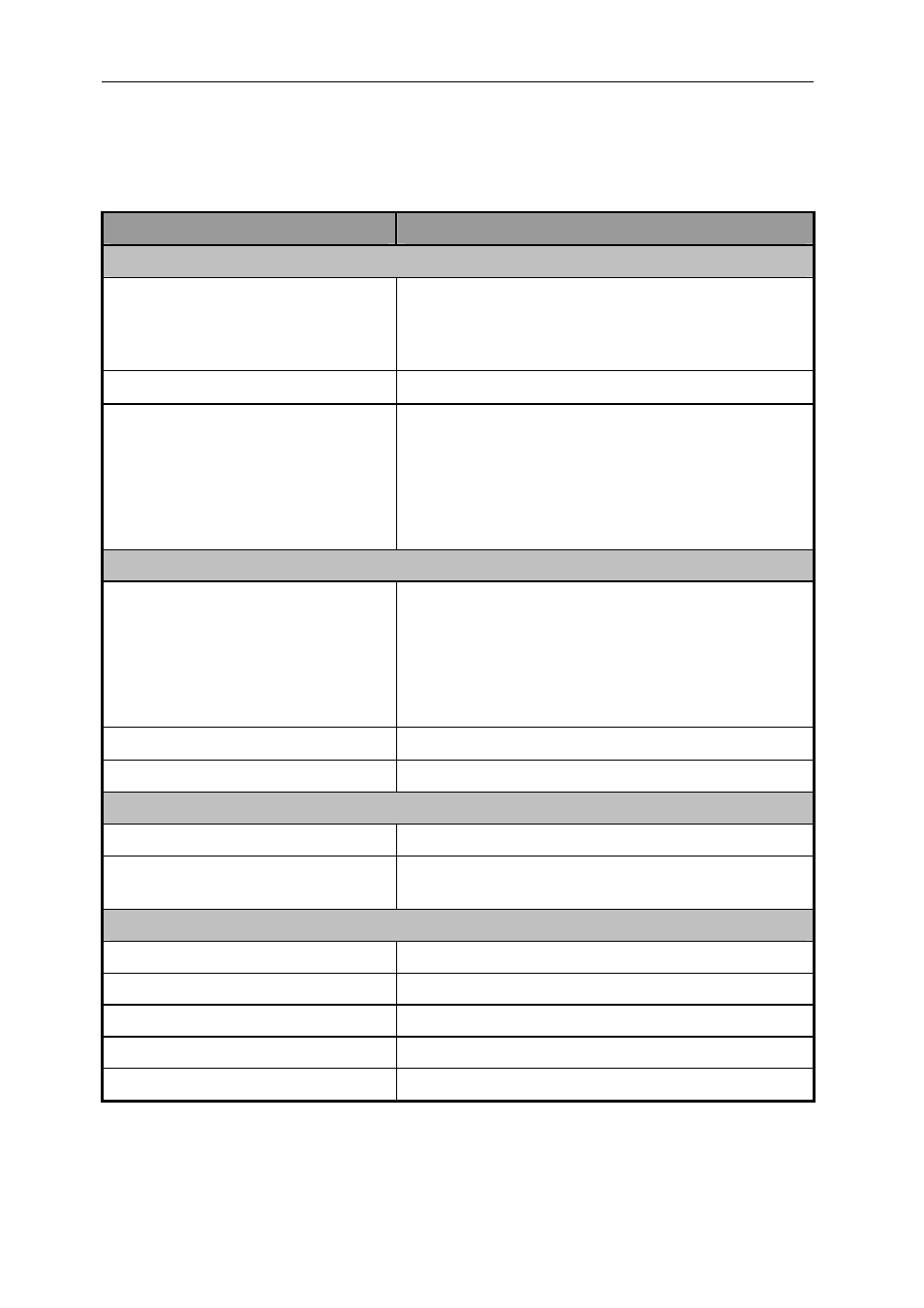

ADC Performance.

Description

Specification

Analogue inputs

Maximum voltage

1.1 Volts peak-to-peak (AC coupling).

2.2 Volts peak-to-peak (DC coupling – Gain 1).

(Specify ADC coupling when placing an order)

Impedance

50

:.

Bandwidth

- No anti-aliasing filter on the board. It is to the

user to set one up if required.

- Input transformers (AC option): 2-775 MHz.

- Input opamps (DC option): 0-320 MHz

- A-to-D converters: 0-250 MHz.

External Clock

Minimum voltage

- DC-coupled input. Requires a External clock

signal centered around 0V.

- 0.2 Volt peak-to-peak minimum.

- Maximum voltage: 3.3 Volts

- Minimum voltage: -3.3 Volts

Impedance

50

:.

Frequency range

30-105 MHz – low jitter.

External Trigger

Frequency Range

0-52.5 MHz.

Signal format

LVTTL (3.3 Volts) format – connected to 3.3V

FPGA – Clamp diodes to 3.3V and Ground.

Characteristics

Resolution

14 bits.

Output format

Binary or 16-bit extended two’s complement.

Maximum sampling frequency

105 MHz.

SFDR

Up to 81dB.

SNR

Up to 63dB.

Figure 5 - ADC Performance.