Interrupts, Interrupt control register – Sundance SMT335E User Manual

Page 12

Version 1.5

Page 12 of 53

SMT335E SMT375E User Manual

Interrupts

The generation of a CPU interrupt by a comm-port, an SDB, or the Global Bus starts

when the FPGA asserts an interrupt condition. For example, this may be the result of

an input FIFO becoming not empty or an output FIFO not full.

The interrupt condition is then further controlled by interrupt condition enables in the

FPGA. If enabled, an asserted interrupt condition will cause one of the CPU’s

external interrupt lines to be asserted and an interrupt event to be latched in the

processor’s Interrupt Flag Register (IFR).

Finally, the processor will be interrupted, providing the interrupt event is enabled in

the processor’s Interrupt Enable Register (IER) and the Global Interrupt Enable (GIE)

is set in the processor’s Control and Status Register (CSR).

The C6000 provides four external interrupt input lines, EXT_INT4, EXT_INT5,

EXT_INT6, and EXT_INT7, which can be driven by a variety of interrupt conditions.

Each external interrupt has a separate interrupt control register (INTCTRLn) where

you set bits to enable the interrupt condition.

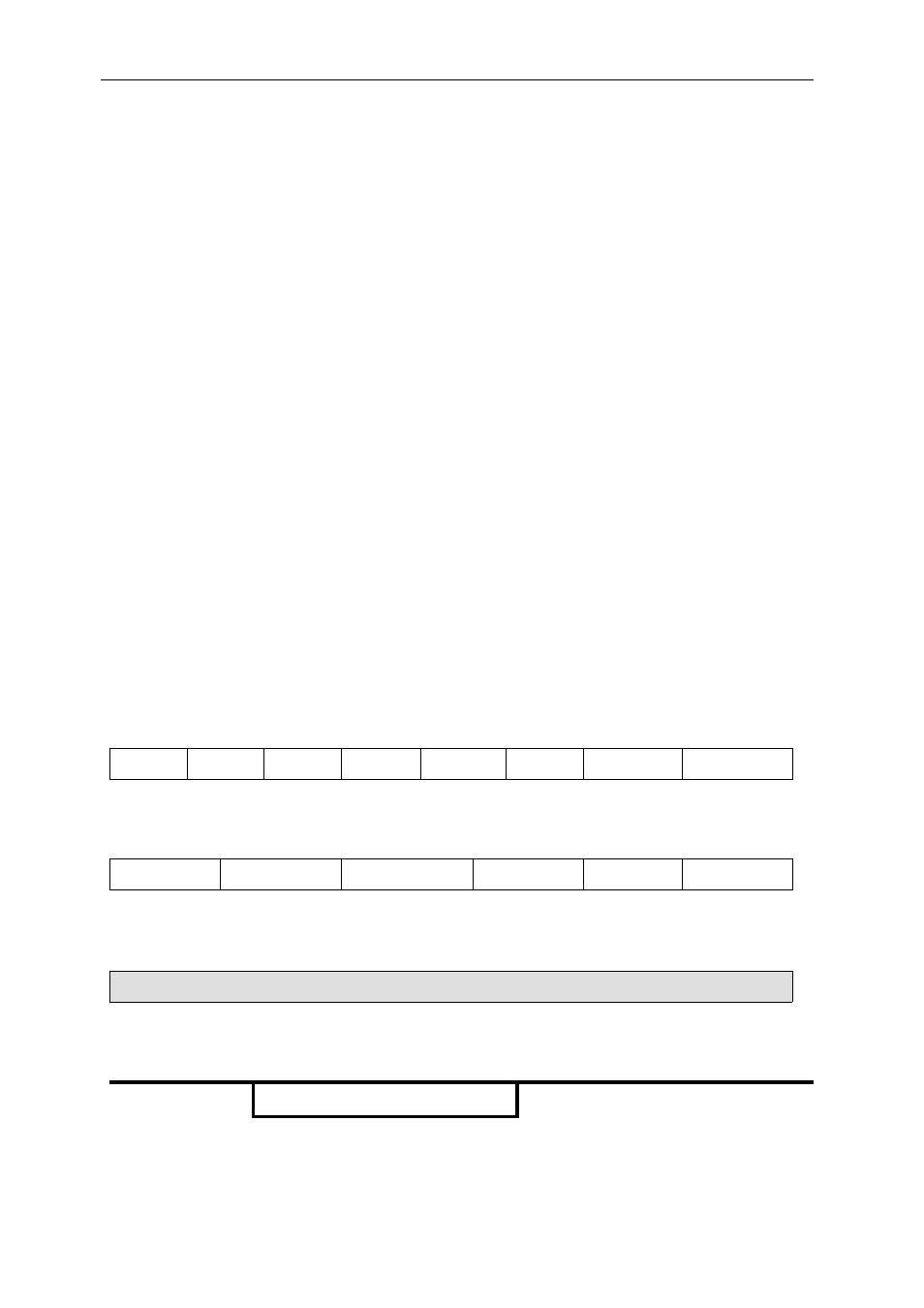

Interrupt Control Register

INTCTRL4 0x03E00000

INTCTRL5 0x03E80000

INTCTRL6 0x03F00000

INTCTRL7 0x03F80000

31–30 29–28 27–26 25–24 23–22 21–20 19–18

17–16

CP0 IE CP1 IE CP2 IE CP3 IE

CP4 IE CP5 IE

SDBA IE

SDBB IE

RW,00 RW,00 RW,00 RW,00 RW,00 RW,00 RW,00

RW,00

15 14 13 12

11

10

GB IE

TCLK1 IE

TCLK0 IE

IIOF2 IE

IIOF1 IE

IIOF0 IE

RW,0 RW,0 RW,0 RW,0

RW,0

RW,0

9–0

RW,0000000000

Field

Description

Interrupt condition selected