Avago Technologies LSI8751D User Manual

Page 292

7-56

Instruction Set of the I/O Processor

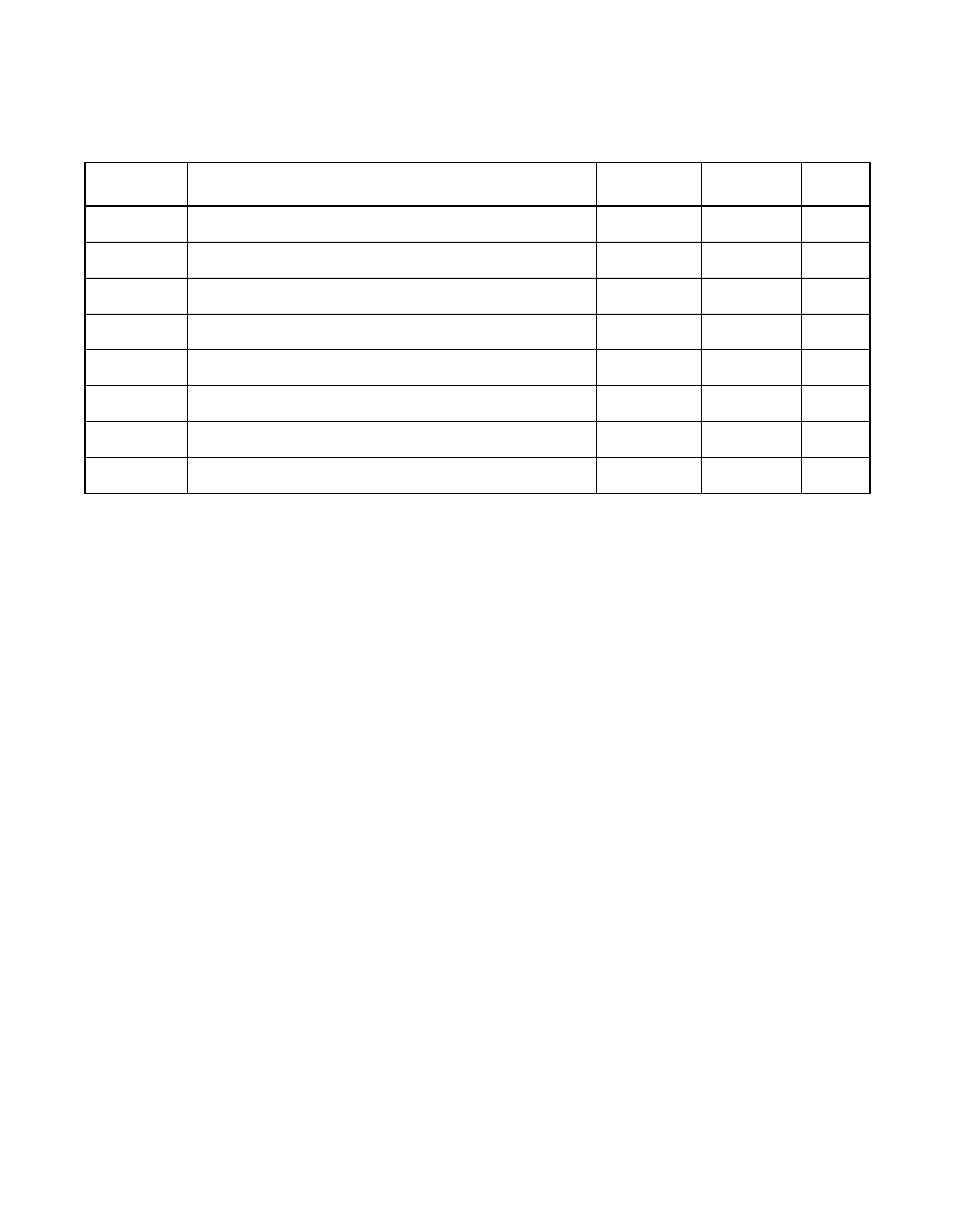

Table 7.28

Ultra SCSI SE Transfers 20.0 Mbytes/s (8-Bit Transfers) or 40.0 Mbytes/s

(16-Bit Transfers), 80 MHz Clock

Symbol

Parameter

Min

Max

Unit

t

1

Send SREQ/ or SACK/ assertion pulse width

16

–

ns

t

2

Send SREQ/ or SACK/ deassertion pulse width

16

–

ns

t

1

Receive SREQ/ or SACK/ assertion pulse width

10

–

ns

t

2

Receive SREQ/ or SACK/ deassertion pulse width

10

–

ns

t

3

Send data setup to SREQ/ or SACK/ asserted

12

–

ns

t

4

Send data hold from SREQ/ or SACK/ asserted

17

–

ns

t

5

Receive data setup to SREQ/ or SACK/ asserted

0

–

ns

t

6

Receive data hold from SREQ/ or SACK/ asserted

6

–

ns

Notes: Transfer period bits (bits [7:5] in the

register) are set to zero and the

Extra Clock Cycle of Data Setup bit (bit 7 in

) is set. For Fast

SCSI, set the TolerANT Enable bit (bit 7 in

). During Ultra SCSI

transfers, the value of the Extend REQ/ ACK Filtering bit (

, bit 1) has

no effect.