Integrate the i/o buffer modules with the, Table 4–35 – Altera ALTDLL User Manual

Page 91

4–55

Chapter 4: Functional Description

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

5. On the Dynamic Delay Chains page, specify the parameters as shown in

.

6. Click Finish. The I/O buffer module

(dqs_iobuf_inst.v/output_dq_iobuf_inst.v/bidir_dq_iobuf_inst.v) is generated.

7. On the File menu, click Save.

Integrate the I/O Buffer Modules with the ALTDQ_DQS modules

To integrate the I/O buffer modules with the ALTDQ_DQS modules, perform the

following steps:

1. Open the test_dq_dqs.bdf file in the Quartus II Block Editor software.

2. To insert the I/O buffer modules, double-click on the Block Editor window. The

Symbol window appears.

3. Under Name, browse to the I/O buffer dqs_iobuf_inst.bsf file.

4. Click OK. The I/O buffer module is inserted into the Block Editor window.

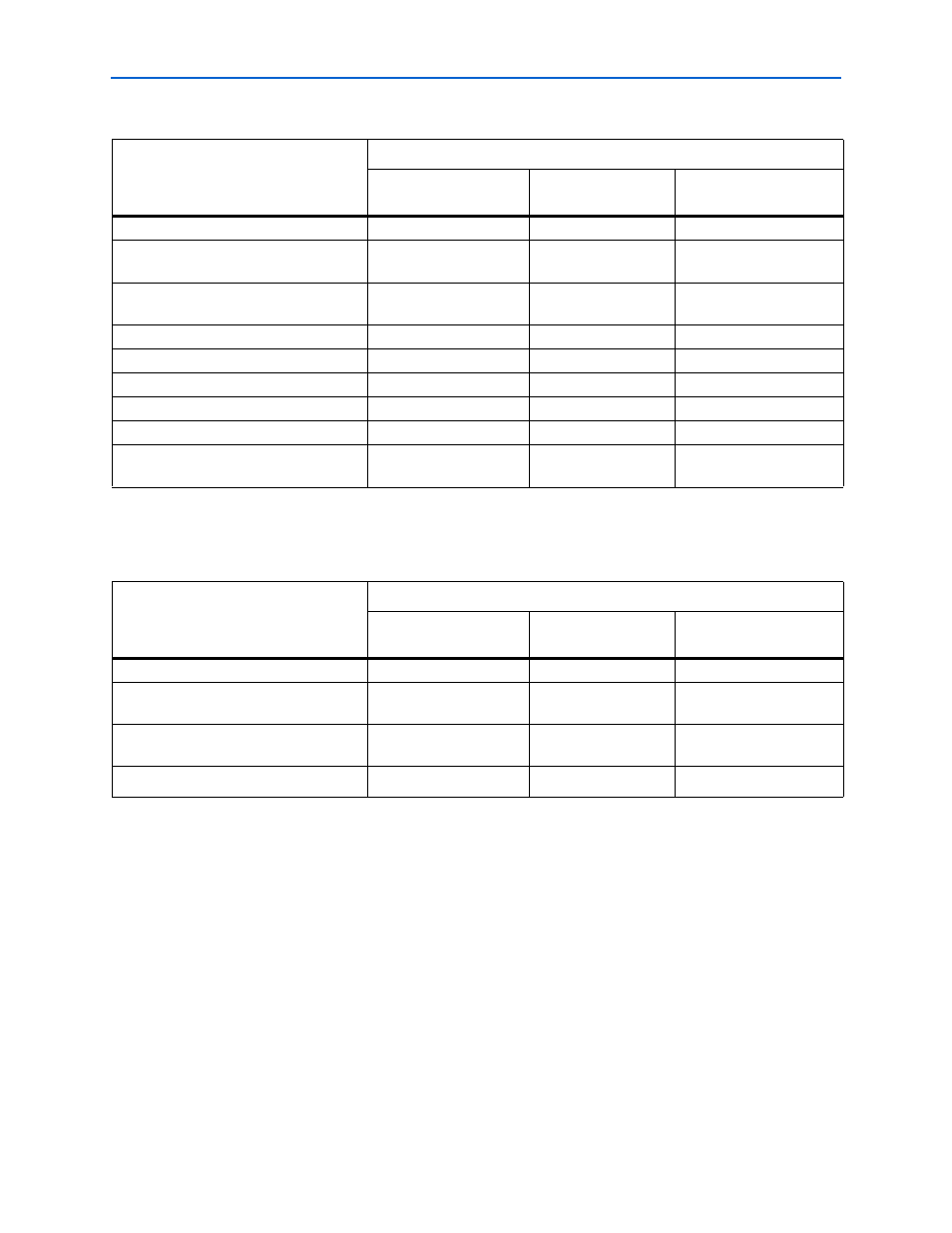

Table 4–35. ALTIOBUF General Settings

Settings

Value

1 bidirectional buffer for

the differential DQS pins

1 output buffer for

the output DQ pins

8 bidirectional buffers for

the bidirectional DQ pins

Currently selected device family

Stratix III

Stratix III

Stratix III

How do you want to configure this

module?

As bidirectional buffer

As output buffer

As bidirectional buffer

What is the number of buffers to be

instantiated?

1

1

8

Use bus hold circuitry

Turned off

Turned off

Turned off

Use differential mode

Turned on

Turned off

Turned off

Use open drain output

Turned off

Turned off

Turned off

Use output enable port

Turned off

Turned on

Turned on

Use dynamic termination control

Turned off

Turned off

Turned off

Use series and parallel termination

control

Turned off

Turned off

Turned off

Table 4–36. ALTIOBUF Dynamic Delay Chain Settings

Settings

Value

1 bidirectional buffer for

the differential DQS pins

1 output buffer for

the output DQ pins

8 bidirectional buffers for

the bidirectional DQ pins

Enable input buffer dynamic delay chain Turned off

Turned off

Turned off

Enable output buffer dynamic delay

chain 1

Turned off

Turned off

Turned off

Enable output buffer dynamic delay

chain 2

Turned off

Turned off

Turned off

Create a ‘clkena’ port

Turned off

Turned off

Turned off